# **Development of Biocompatible Parylene Neurocages for Action Potential Stimulation and Recording**

Thesis by

**Angela Colleen Tooker**

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

2007

(Defended May 16, 2007)

© 2007

Angela Colleen Tooker

All Rights Reserved

# Acknowledgements

I would like to dedicate this thesis to my parents and my sister, Michelle. For their unwavering support and assistance in so many ways over the years, I am extremely grateful.

Thanks also to my advisors Yu-Chong Tai and Jerry Pine for their advice and direction in completing this work. I would also like to thank the members of the Caltech Micromachining Lab, most especially Wen Li, Damien Rodger, Ellis Meng, Scott Miserendino, Nicholas Lo, and Quoc Quach, for their help in designing and fabricating the many, many versions of the neurocage. In addition, I would like to thank Jon Erickson and Gary Chow for their many hours of neuron culturing and helping to design and re-design the neurocages. Finally, I would also like to thank Trevor Roper and Pat Koen.

# Abstract

Neurons, and the neural networks they form, are at the heart of our biological and cognitive functions. Traditional *in vitro* techniques for studying neural networks use two-dimensional multi-electrode arrays. While furthering the study of neural networks, the inherent mobility of the neurons and the lack of specificity between neurons and electrodes can limit the use of these arrays. Initial work, the neuro-well, eliminated these problems by physically trapping individual neurons in wells. While neural networks were formed and action potentials recorded with arrays of neuro-wells, the bulk micromachining techniques required a complex fabrication process, with limited scalability and a low yield, thus inhibiting their further development.

Parylene neurocages counteract these difficulties by using surface micromachined structures to trap neurons in close proximity to electrodes, without inhibiting their growth. The use of surface micromachining techniques minimizes the fabrication and scaling complexities, improving the device yield. The neurocages can be fabricated on either glass or silicon substrates, with a variety of electrical insulation materials, including Parylene and silicon-nitride. Parylene is a biocompatible polymer that is non-toxic, extremely inert, and resistant to moisture and most chemicals. Its conformal deposition makes it easy to fabricate 3D structures like the neurocage. Parylene is transparent, allowing the neurons to be easily seen.

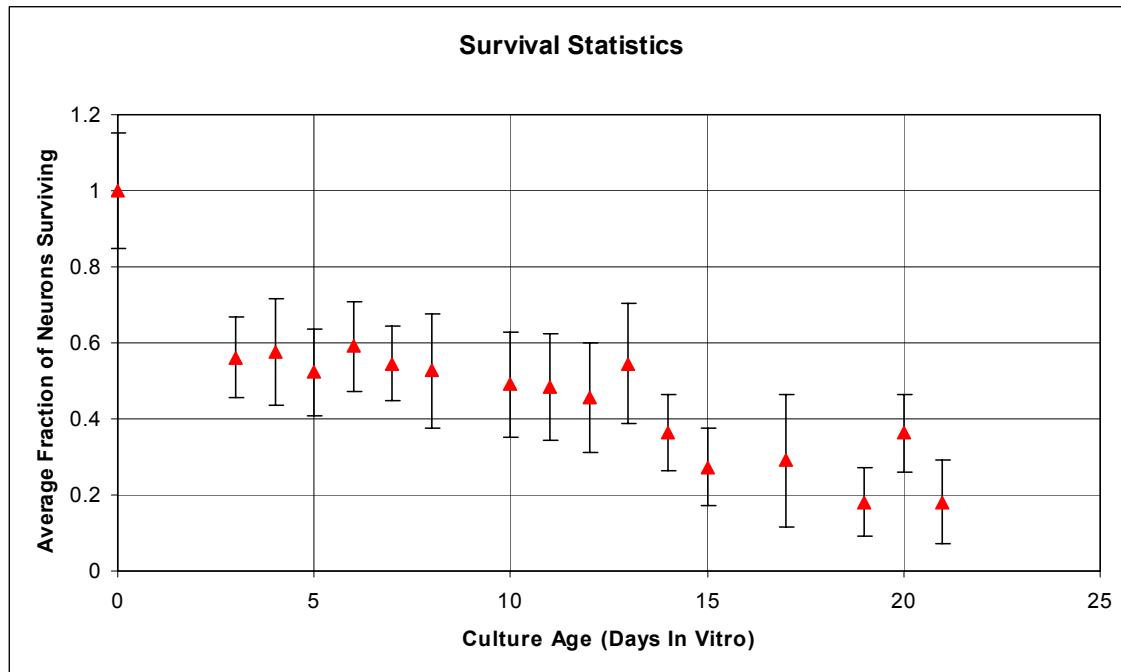

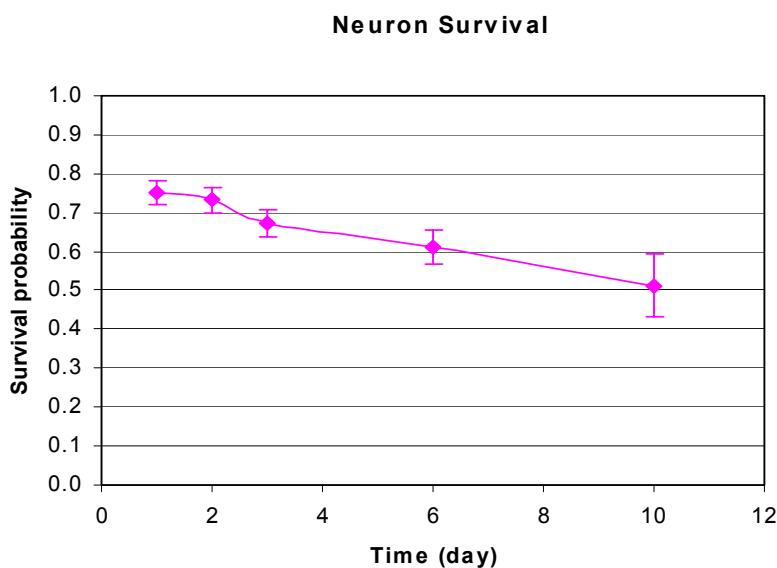

Individual neurons are placed into the neurocages, either manually with a pressure-driven micropipette or automatically with a laser tweezers system. The neurocages have openings to allow the neurites to extend out of the neurocages and form synaptic connections with their neighboring neurons. Each neurocage has its own electrode, which is platinized to increase its capacitance. Successful growth of neural networks has been achieved using arrays of neurocages with Parylene and silicon-nitride insulation on both silicon and glass substrates. These neurocages have a long-term cell survival rate of ~ 50% after 3 weeks and have proven 99% effective in trapping neurons. The neurons inside the neurocages have been successfully stimulated, with both current and voltage pulses. Action potentials, both spontaneous and resulting from a current stimulus, have been recorded from neurons comprising the neural networks.

# Table of Contents

|                                                  |             |

|--------------------------------------------------|-------------|

| <b>Acknowledgements.....</b>                     | <b>iii</b>  |

| <b>Abstract.....</b>                             | <b>iv</b>   |

| <b>Table of Contents.....</b>                    | <b>vi</b>   |

| <b>List of Figures.....</b>                      | <b>xi</b>   |

| <b>List of Tables.....</b>                       | <b>xvii</b> |

| <b>1. Neurons and Neural Networks.....</b>       | <b>1</b>    |

| <b>1.1. Neurons.....</b>                         | <b>1</b>    |

| <b>1.2. Patch-Clamp Recording Technique.....</b> | <b>3</b>    |

| <b>1.3. Multi-Electrode Arrays (MEAs).....</b>   | <b>3</b>    |

| <b>1.4. Neuro-Well.....</b>                      | <b>5</b>    |

| <b>1.5. Neurocage.....</b>                       | <b>6</b>    |

| <b>2. MEMS Fabrication Technologies.....</b>     | <b>8</b>    |

| <b>2.1. Fabrication Technologies.....</b>        | <b>9</b>    |

|                                                              |           |

|--------------------------------------------------------------|-----------|

| <b>2.1.1.</b> Photolithography.....                          | <b>10</b> |

| <b>2.1.2.</b> Oxidation.....                                 | <b>12</b> |

| <b>2.1.2.1.</b> Thermal Oxidation.....                       | <b>13</b> |

| <b>2.1.2.2.</b> Sputtering.....                              | <b>13</b> |

| <b>2.1.3.</b> Etching.....                                   | <b>14</b> |

| <b>2.1.3.1.</b> Wet Etchants.....                            | <b>15</b> |

| <b>2.1.3.2.</b> Dry Etchants.....                            | <b>16</b> |

| <b>2.1.4.</b> Evaporation.....                               | <b>17</b> |

| <b>2.1.5.</b> Chemical Vapor Deposition (CVD).....           | <b>18</b> |

| <b>2.2.</b> Parylene.....                                    | <b>20</b> |

| <b>2.2.1.</b> Parylene Deposition.....                       | <b>20</b> |

| <b>2.2.2.</b> Parylene Properties.....                       | <b>22</b> |

| <br>                                                         |           |

| <b>3.</b> Neurocages on Silicon without Electrodes.....      | <b>24</b> |

| <b>3.1.</b> Design Components.....                           | <b>25</b> |

| <b>3.1.1.</b> Anchors.....                                   | <b>25</b> |

| <b>3.1.2.</b> Tunnels and Chimneys.....                      | <b>28</b> |

| <b>3.1.2.1.</b> Sacrificial Materials.....                   | <b>29</b> |

| <b>3.1.3.</b> Neurocage Arrays.....                          | <b>31</b> |

| <b>3.2.</b> Aluminum Sacrificial Material.....               | <b>31</b> |

| <b>3.2.1.</b> Fabrication.....                               | <b>31</b> |

| <b>3.2.2.</b> Culturing Results.....                         | <b>37</b> |

| <b>3.3.</b> Hard-Baked Photoresist Sacrificial Material..... | <b>39</b> |

|                                                              |           |

|--------------------------------------------------------------|-----------|

| <b>3.3.1.</b> Fabrication.....                               | <b>39</b> |

| <b>3.4.</b> Soft-Baked Photoresist Sacrificial Material..... | <b>41</b> |

| <b>3.4.1.</b> Fabrication.....                               | <b>42</b> |

| <b>3.4.2.</b> Culturing Results.....                         | <b>49</b> |

| <b>3.5.</b> Future Work.....                                 | <b>52</b> |

| <br>                                                         |           |

| <b>4. Neurocages on Silicon with Electrodes.....</b>         | <b>53</b> |

| <b>4.1.</b> Insulation Materials.....                        | <b>53</b> |

| <b>4.2.</b> Parylene-C and the Aluminum Etch Stop.....       | <b>54</b> |

| <b>4.2.1.</b> Closed Tunnels.....                            | <b>55</b> |

| <b>4.2.2.</b> Roughened Parylene-C Insulation.....           | <b>56</b> |

| <b>4.2.3.</b> Aluminum Etch Stop.....                        | <b>57</b> |

| <b>4.3.</b> Moats, Curtains, and Melted Chimneys.....        | <b>58</b> |

| <b>4.3.1.</b> Moats.....                                     | <b>58</b> |

| <b>4.3.2.</b> Curtains.....                                  | <b>59</b> |

| <b>4.3.3.</b> Melted Chimneys.....                           | <b>63</b> |

| <b>4.3.4.</b> Resulting Neurocages.....                      | <b>64</b> |

| <b>4.4.</b> Parylene-C Bubbling.....                         | <b>64</b> |

| <b>4.5.</b> Anchors.....                                     | <b>67</b> |

| <b>4.6.</b> Neurocage Design.....                            | <b>68</b> |

| <b>4.6.1.</b> Neuron Escape Rate.....                        | <b>68</b> |

| <b>4.6.2.</b> Tunnel Sacrificial Material.....               | <b>71</b> |

| <b>4.6.3.</b> Platinized Electrodes.....                     | <b>73</b> |

|                                                                           |            |

|---------------------------------------------------------------------------|------------|

| <b>4.6.3.1.</b> Chimney Diameter.....                                     | <b>73</b>  |

| <b>4.6.3.2.</b> Parylene-C Insulation Thickness.....                      | <b>74</b>  |

| <b>4.6.3.3.</b> Neurocage Electrode Location and Anchors.....             | <b>74</b>  |

| <b>4.6.4.</b> Final Neurocage Design and Electrode Layout.....            | <b>76</b>  |

| <b>4.7.</b> Fabrication Process.....                                      | <b>77</b>  |

| <b>4.8.</b> Culturing Results.....                                        | <b>94</b>  |

| <b>4.9.</b> Electrical Stimulation and Recording.....                     | <b>97</b>  |

| <b>4.10.</b> Long-Term Impedance Testing.....                             | <b>100</b> |

| <b>4.11.</b> Future Work.....                                             | <b>102</b> |

| <br>                                                                      |            |

| <b>5.</b> Neurocages on Glass with Electrodes.....                        | <b>105</b> |

| <b>5.1.</b> Laser Tweezers.....                                           | <b>105</b> |

| <b>5.2.</b> Design and Fabrication.....                                   | <b>107</b> |

| <b>5.2.1.</b> Glass Slides.....                                           | <b>107</b> |

| <b>5.2.2.</b> Design.....                                                 | <b>108</b> |

| <b>5.2.2.1.</b> Electrodes.....                                           | <b>109</b> |

| <b>5.2.2.2.</b> Anchors.....                                              | <b>110</b> |

| <b>5.2.3.</b> Fabrication with Parylene-C Insulation.....                 | <b>112</b> |

| <b>5.2.4.</b> Fabrication with Low-Stress Silicon-Nitride Insulation..... | <b>125</b> |

| <b>5.3.</b> Neuron Loading and Culturing.....                             | <b>134</b> |

| <b>5.4.</b> Future Work.....                                              | <b>135</b> |

| <br>                                                                      |            |

| <b>6.</b> Conclusions.....                                                | <b>137</b> |

|                 |     |

|-----------------|-----|

| References..... | 141 |

|-----------------|-----|

|                                                                                               |     |

|-----------------------------------------------------------------------------------------------|-----|

| Appendix I. Detailed Fabrication Process for Neurocages on Silicon without<br>Electrodes..... | 149 |

|-----------------------------------------------------------------------------------------------|-----|

|                                                                                                                       |     |

|-----------------------------------------------------------------------------------------------------------------------|-----|

| Appendix II. Detailed Fabrication Process for Neurocages on Silicon with<br>Electrodes and Parylene-C Insulation..... | 157 |

|-----------------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                                                        |     |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Appendix III. Detailed Fabrication Process for Neurocages on Silicon with<br>Electrodes and Low-Stress Silicon-Nitride Insulation..... | 177 |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                                     |     |

|---------------------------------------------------------------------------------------------------------------------|-----|

| Appendix IV. Detailed Fabrication Process for Neurocages on Glass with Electrodes<br>and Parylene-C Insulation..... | 193 |

|---------------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                                                    |     |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| Appendix V. Detailed Fabrication Process for Neurocages on Glass with Electrodes<br>and Low-Stress Silicon-Nitride Insulation..... | 209 |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

# List of Figures

|                                                                                                                                                                                               |           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

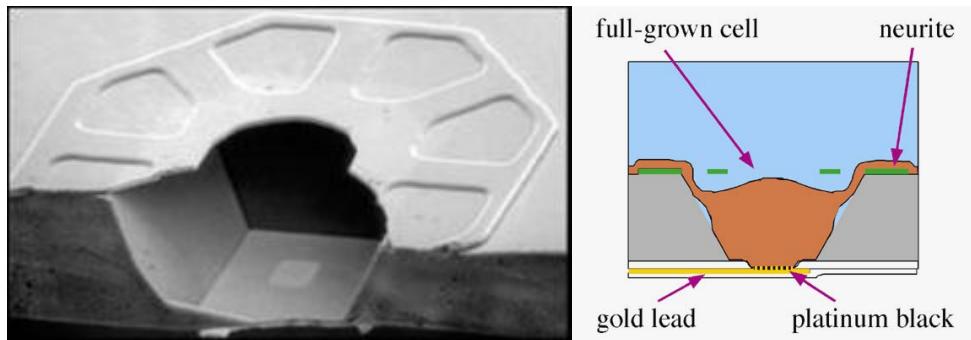

| <b>1-1.</b> Scanning electron micrograph of a cross-section of a neuro-well. Illustration of a neuron inside a neuro-well.....                                                                | <b>5</b>  |

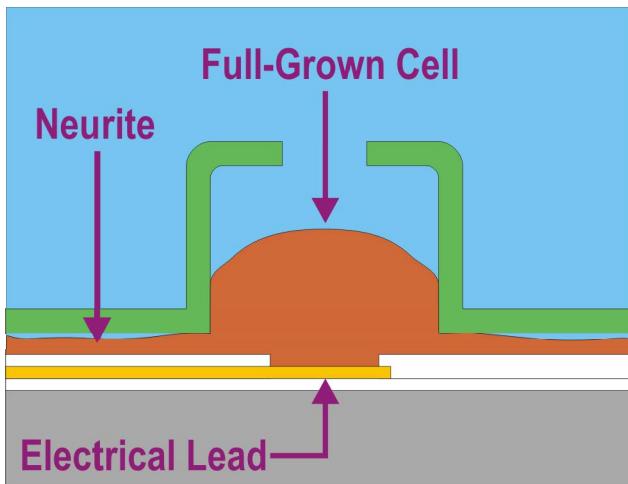

| <b>1-2.</b> Illustration of a neuron inside the neurocage.....                                                                                                                                | <b>7</b>  |

|                                                                                                                                                                                               |           |

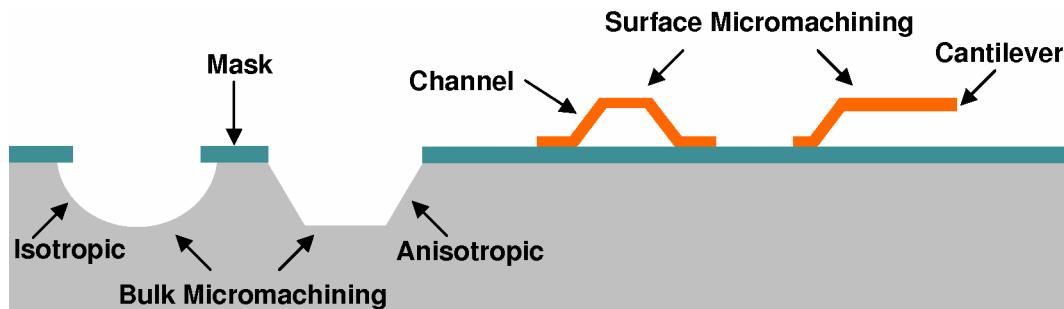

| <b>2-1.</b> Examples of bulk micromachining and surface micromachining.....                                                                                                                   | <b>9</b>  |

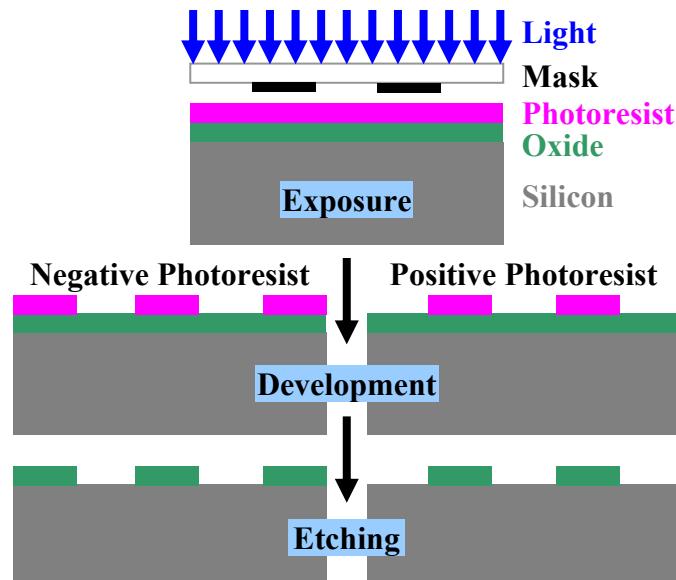

| <b>2-2.</b> Illustration of the photolithography process for both positive and negative photoresists.....                                                                                     | <b>11</b> |

| <b>2-3.</b> Illustration of the differences between isotropic and anisotropic wet etching.....                                                                                                | <b>15</b> |

| <b>2-4.</b> Chemical structures for the three most common types of Parylene.....                                                                                                              | <b>20</b> |

| <b>2-5.</b> Schematic of the Parylene deposition system and the associated chemicals.....                                                                                                     | <b>21</b> |

|                                                                                                                                                                                               |           |

| <b>3-1.</b> Two different neurocage designs: long tunnels and short tunnels.....                                                                                                              | <b>25</b> |

| <b>3-2.</b> Scanning electron micrograph of a tunnel and anchors etched with $\text{XeF}_2$ .....                                                                                             | <b>26</b> |

| <b>3-3.</b> Scanning electron micrograph of an anchor etched into silicon and filled in with Parylene-C.....                                                                                  | <b>27</b> |

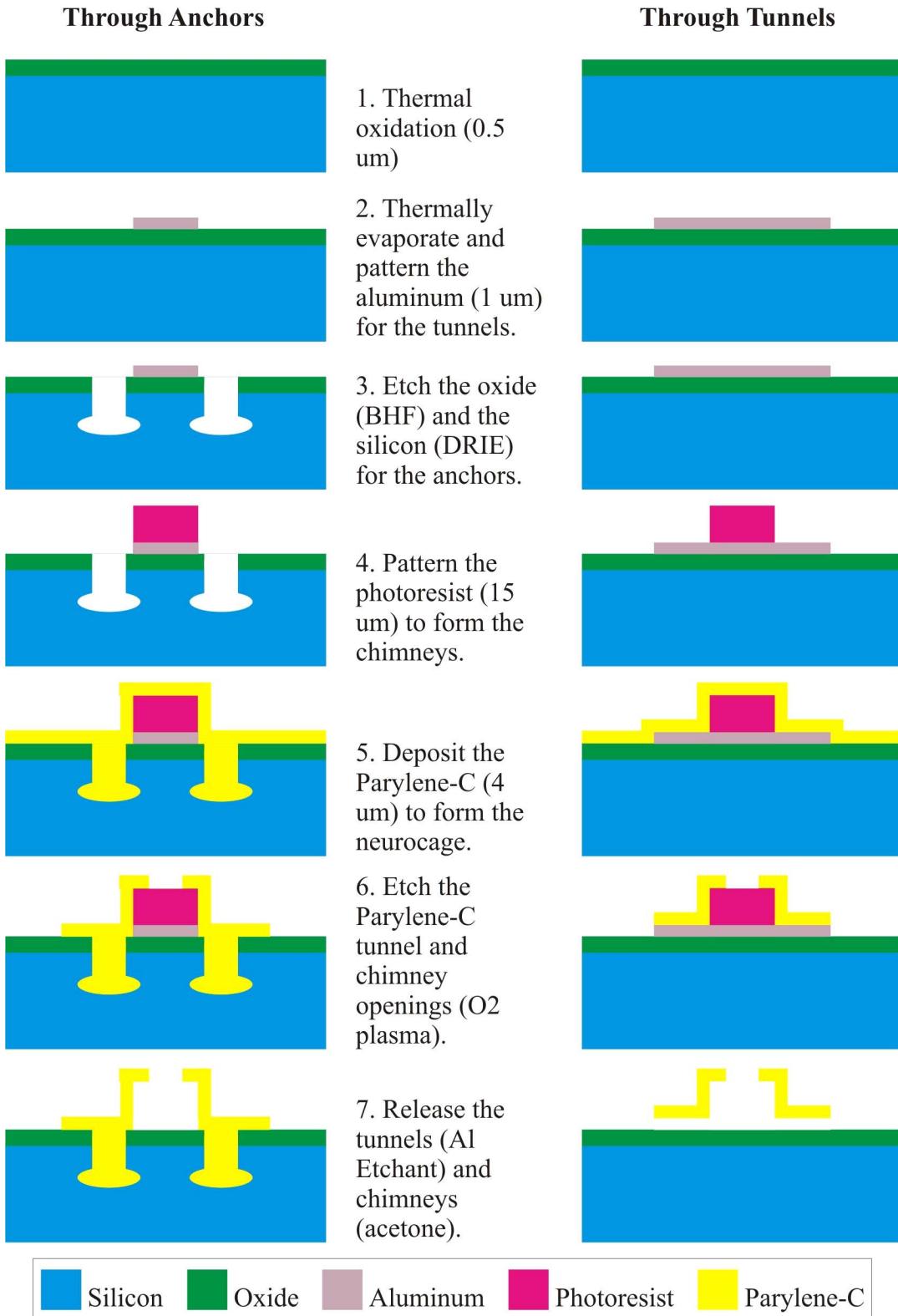

| <b>3-4.</b> Process flow for the neurocages on silicon with aluminum as the sacrificial material for the tunnels and soft-baked photoresist as the sacrificial material for the chimneys..... | <b>33</b> |

| <b>3-5.</b> Illustration of a common problem when doing metal lift-off with a single layer of photoresist and the results when using two layer of photoresist.....                            | <b>34</b> |

|                                                                                                                                                      |           |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>3-6.</b> Optical images showing the patterned sacrificial aluminum for the tunnels.....                                                           | <b>35</b> |

| <b>3-7.</b> Optical images showing the anchors that have been etched into the silicon.....                                                           | <b>35</b> |

| <b>3-8.</b> Optical image showing the photoresist chimneys.....                                                                                      | <b>36</b> |

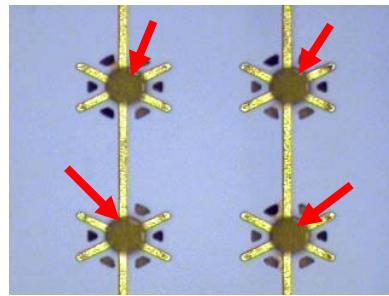

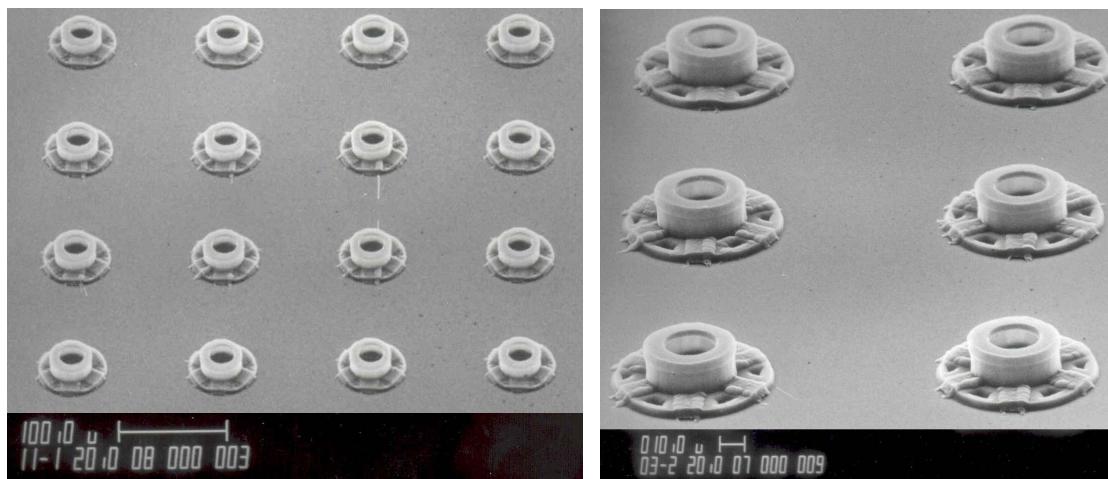

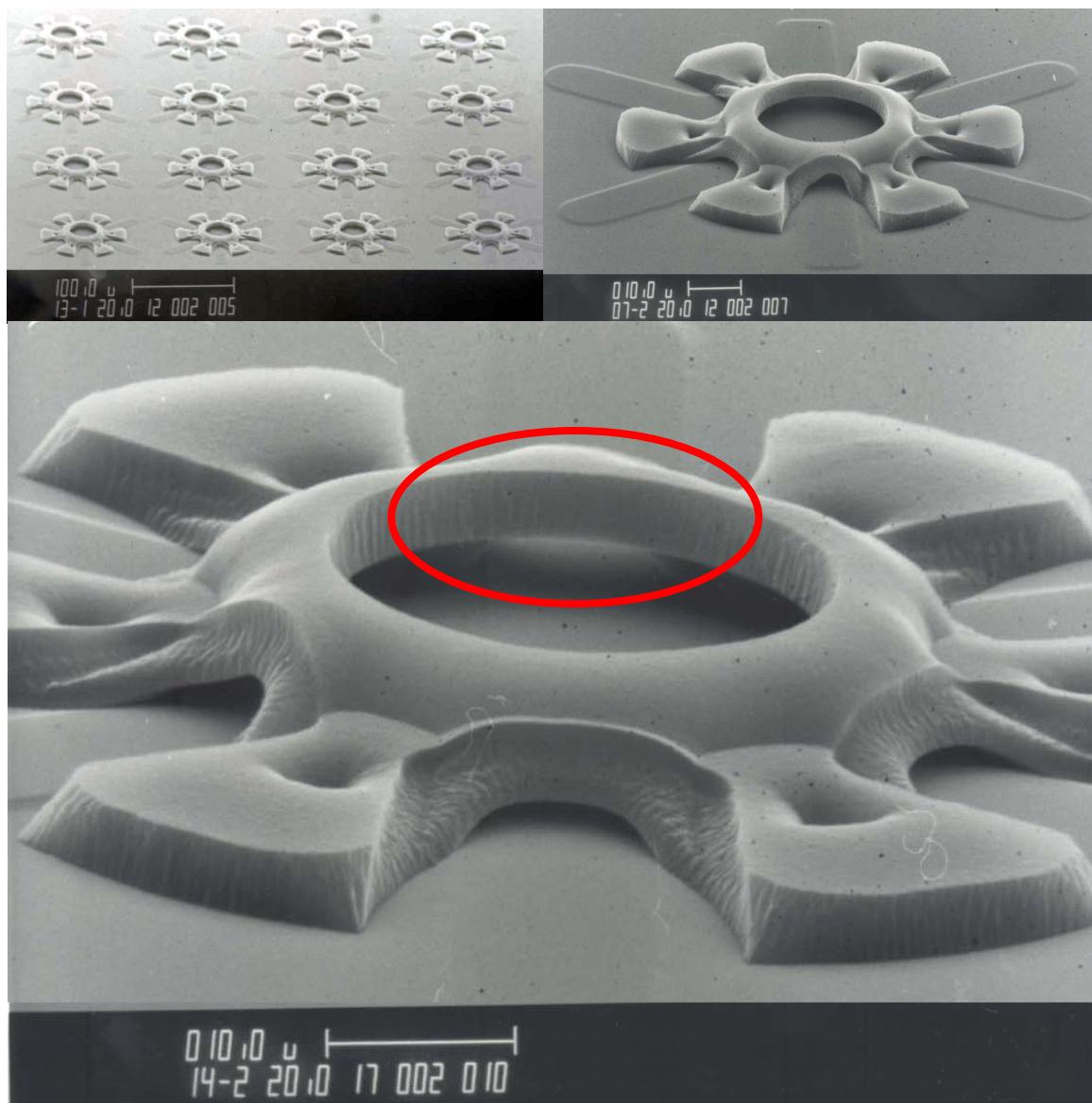

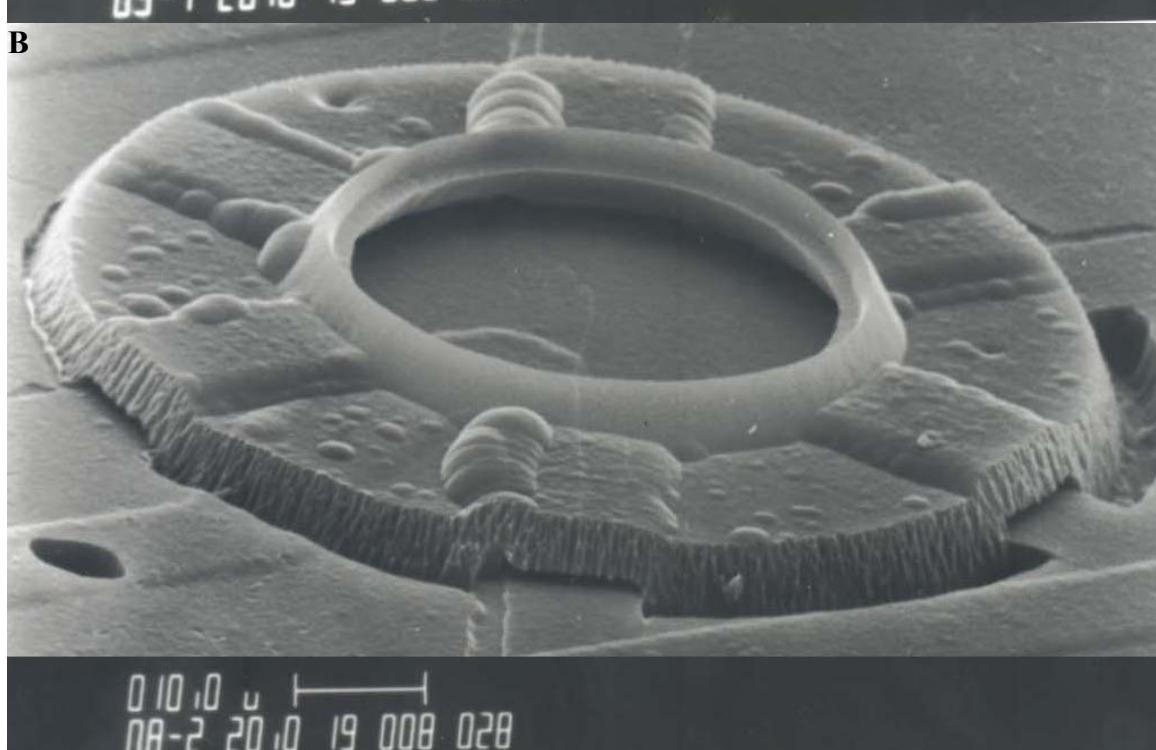

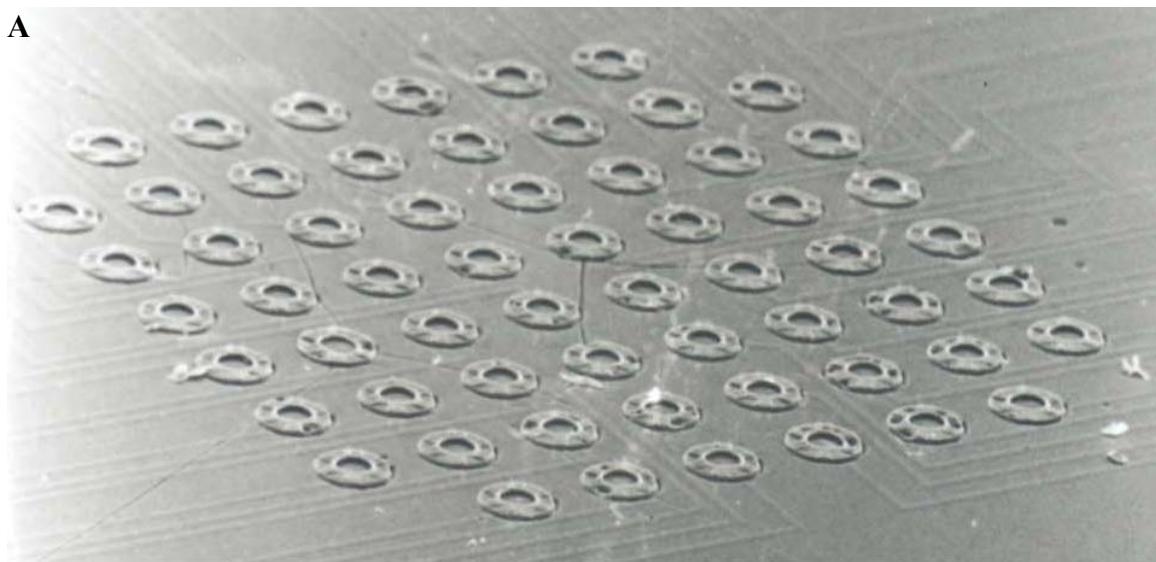

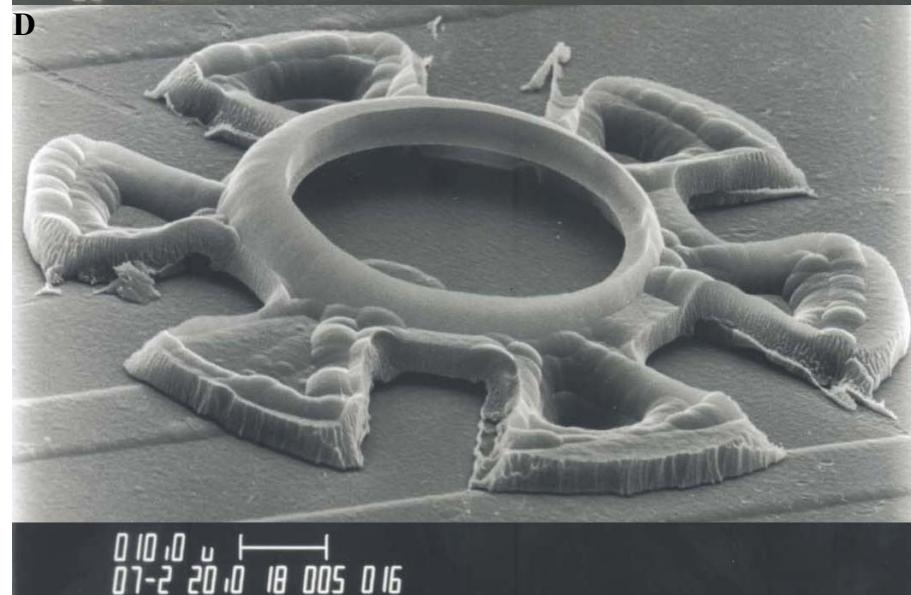

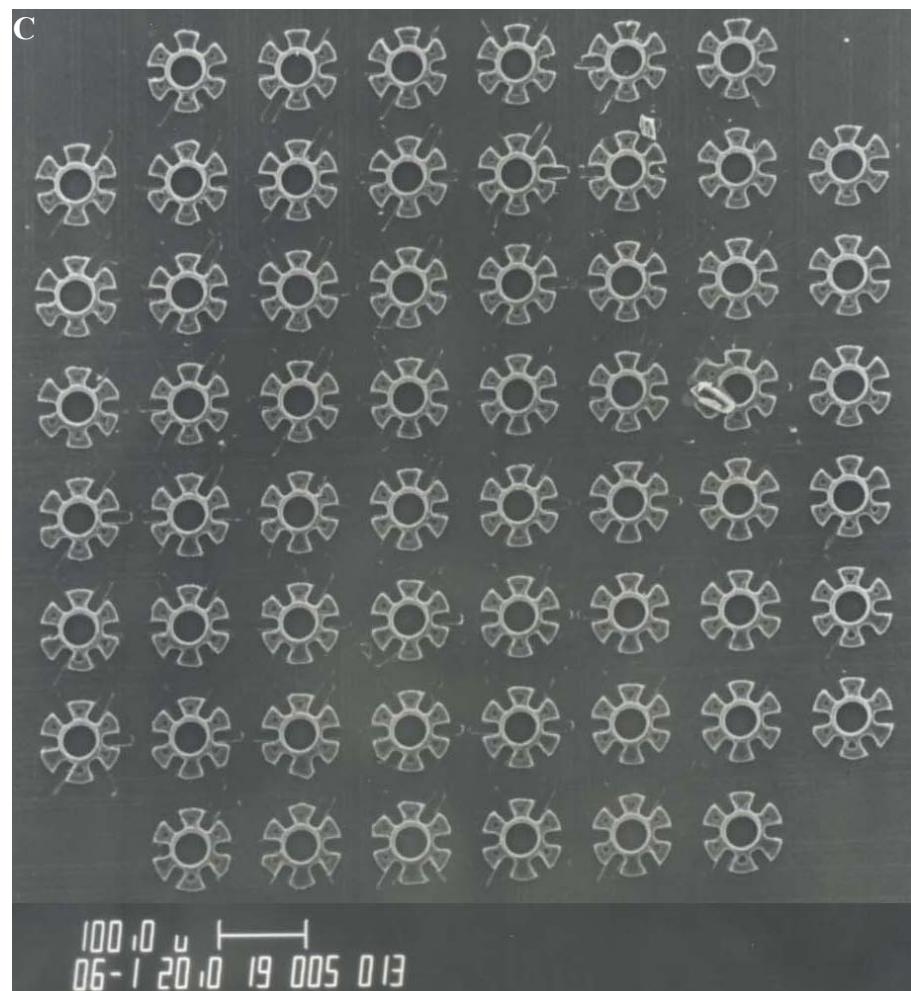

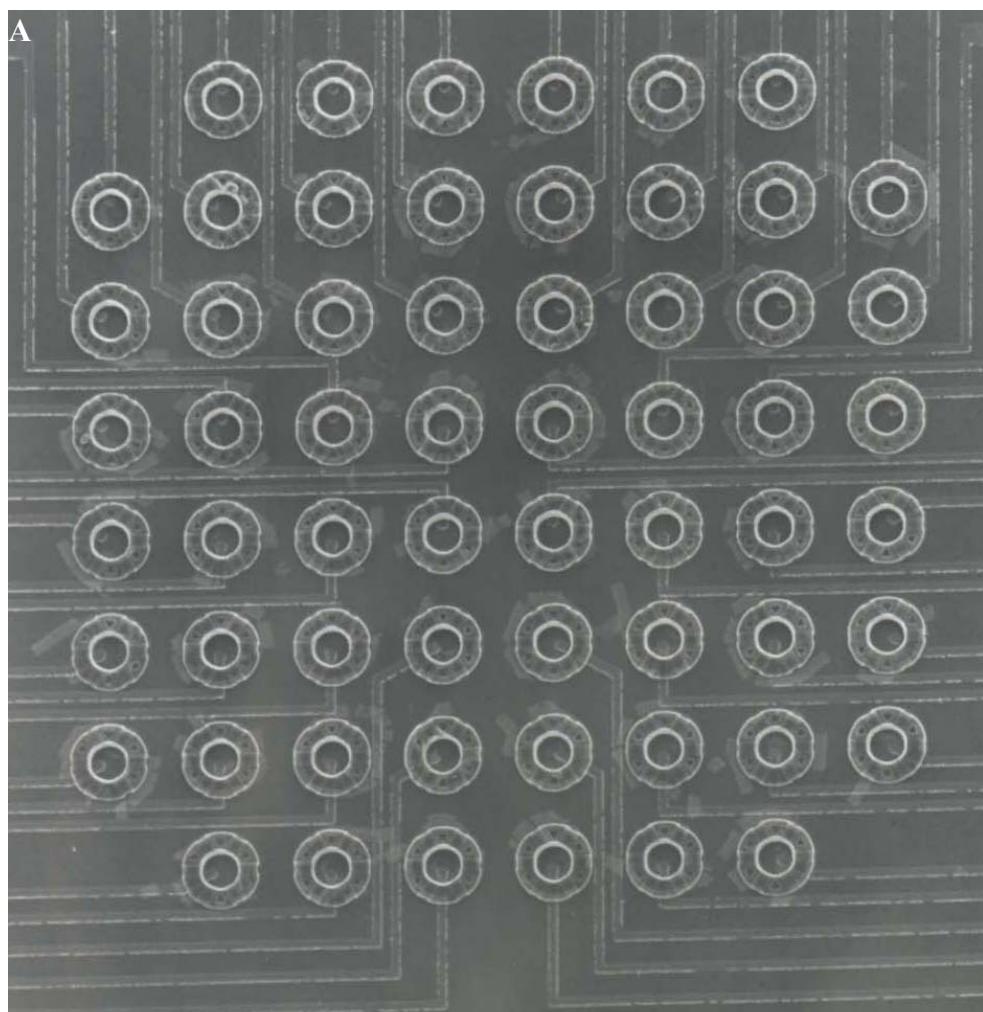

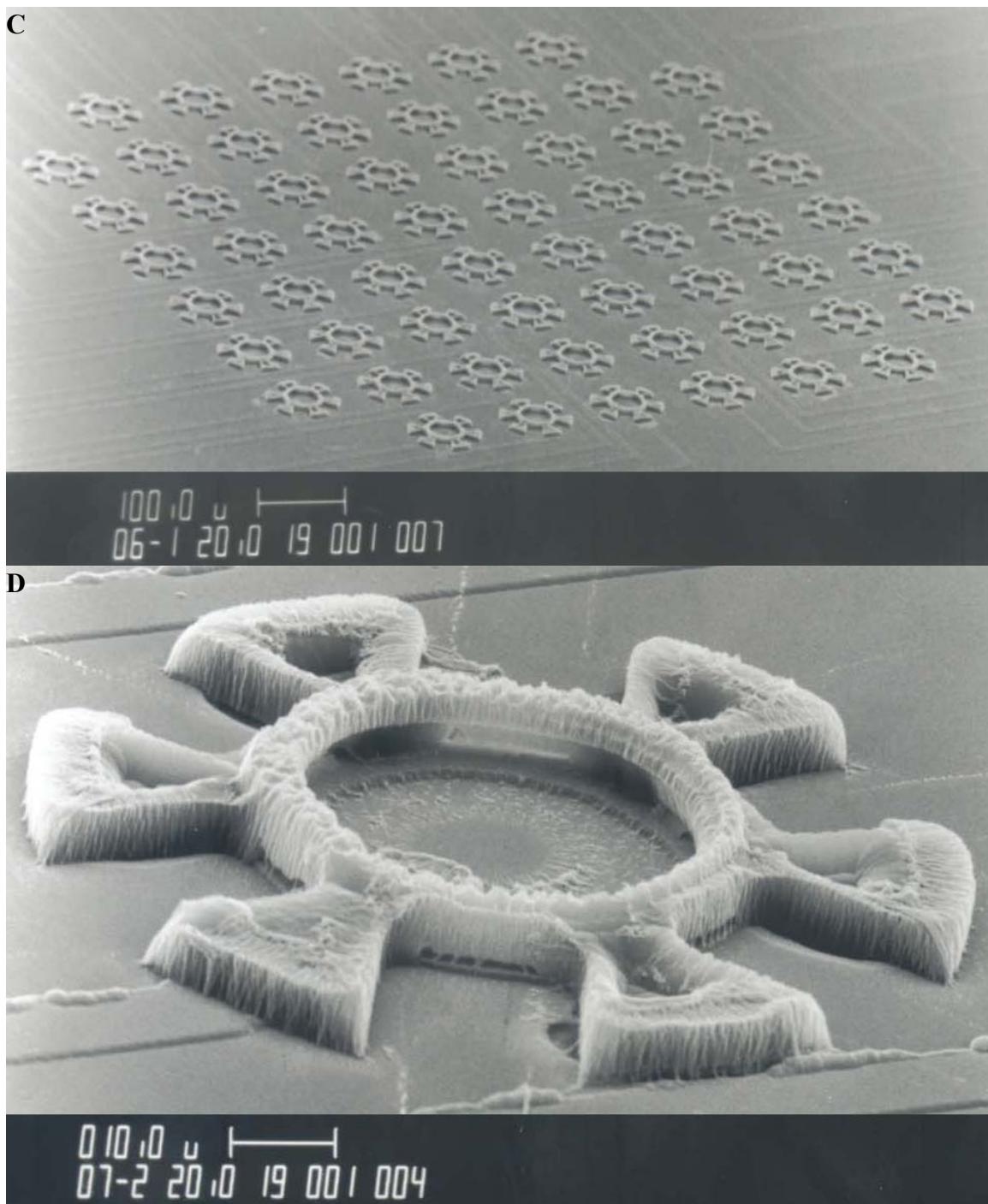

| <b>3-9.</b> SEMs of neurocage arrays.....                                                                                                            | <b>37</b> |

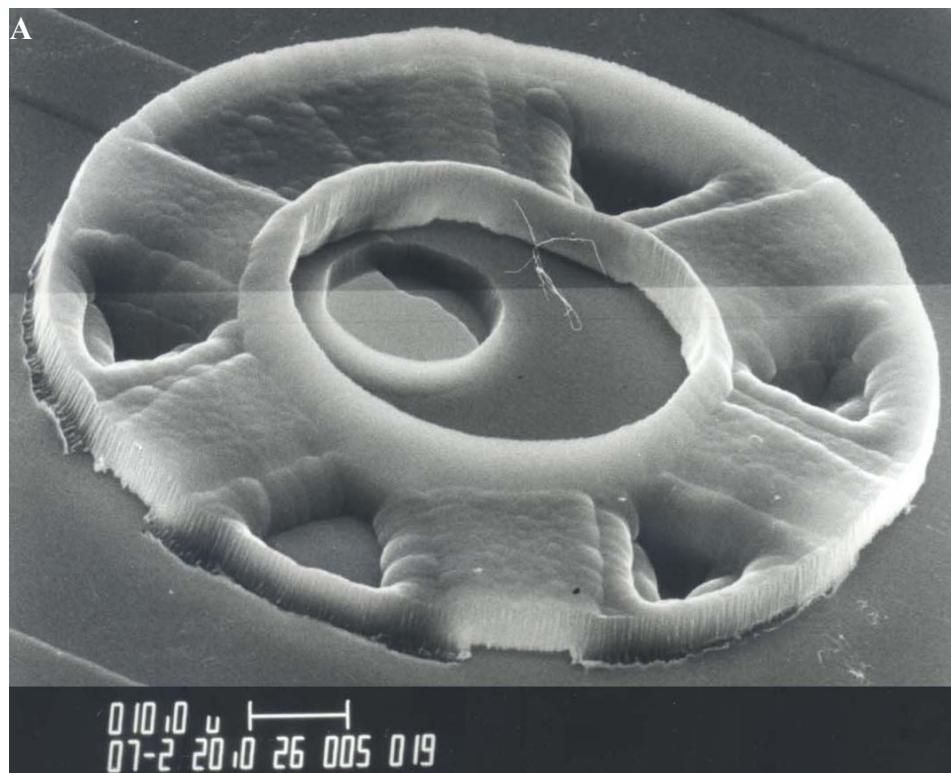

| <b>3-10.</b> SEM of a single neurocage.....                                                                                                          | <b>38</b> |

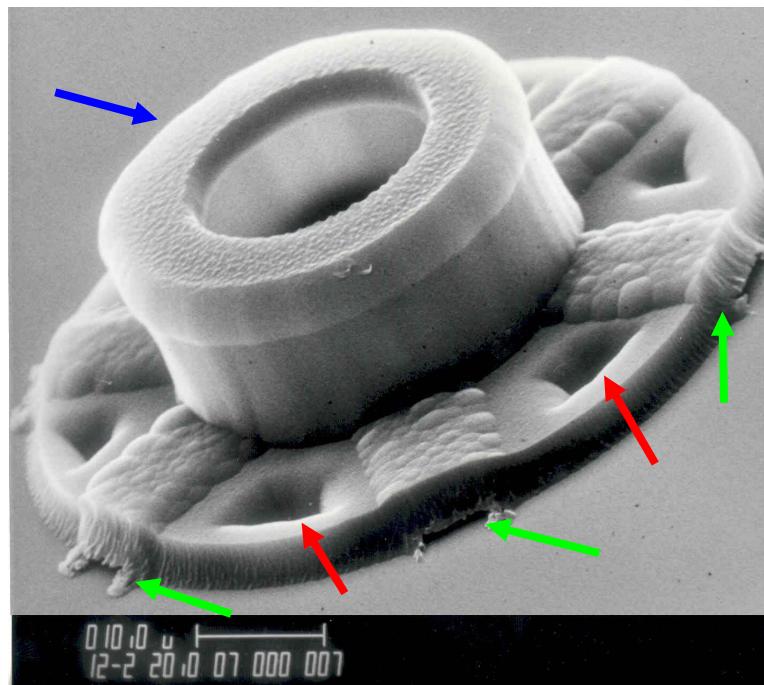

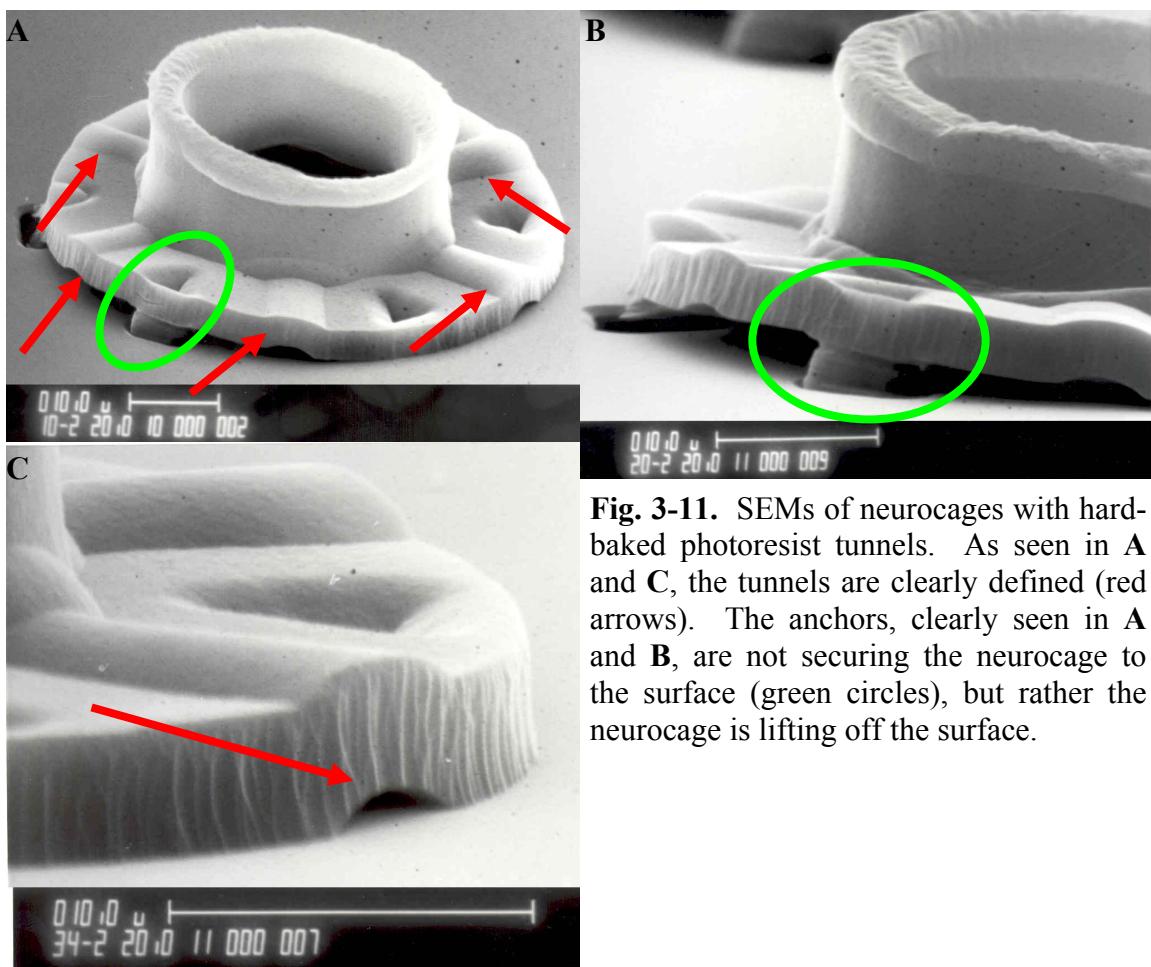

| <b>3-11.</b> SEMs of neurocages with hard-baked photoresist tunnels.....                                                                             | <b>40</b> |

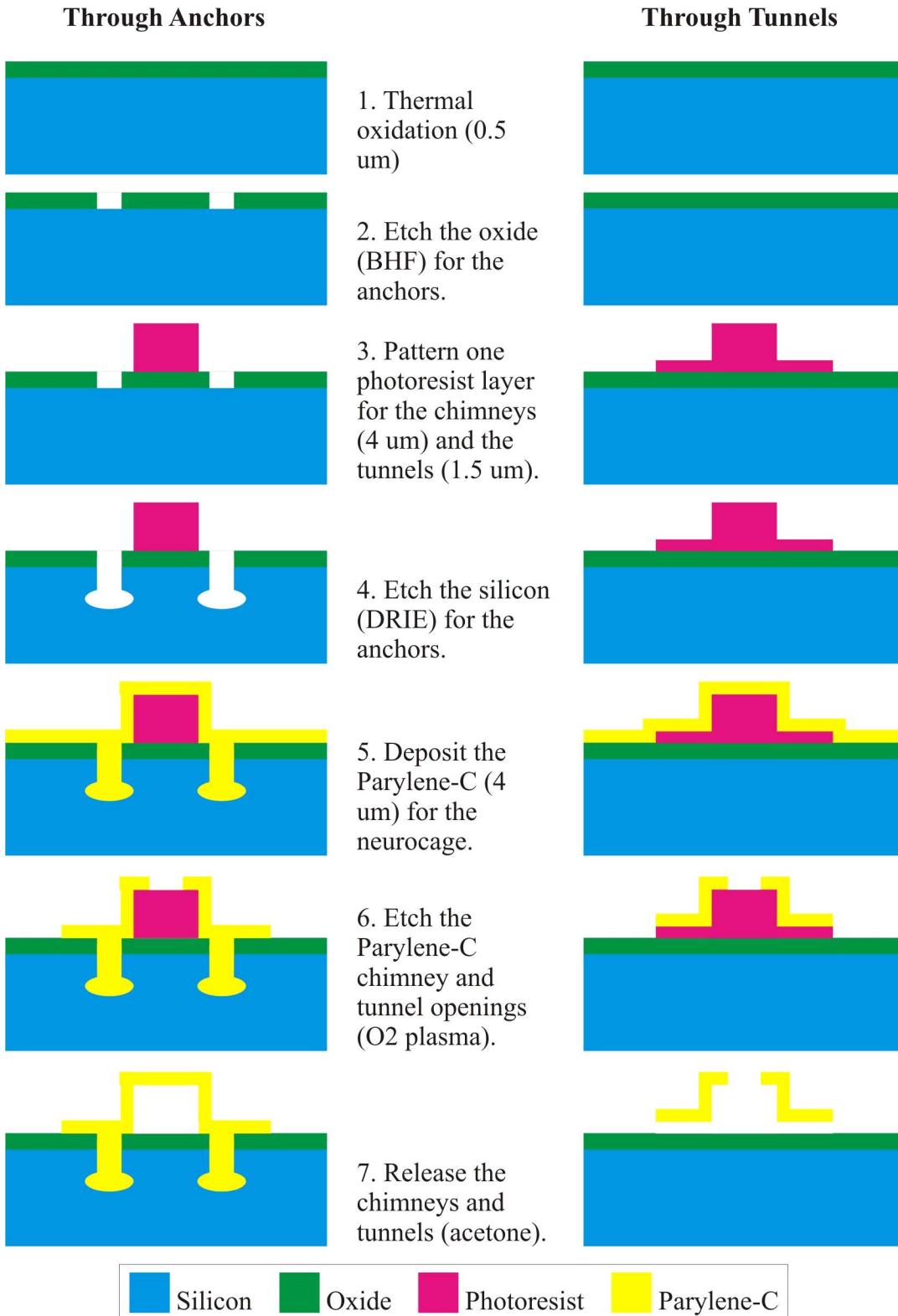

| <b>3-12.</b> Process flow for the neurocages on silicon with soft-baked photoresist as the<br>sacrificial material for the tunnels and chimneys..... | <b>43</b> |

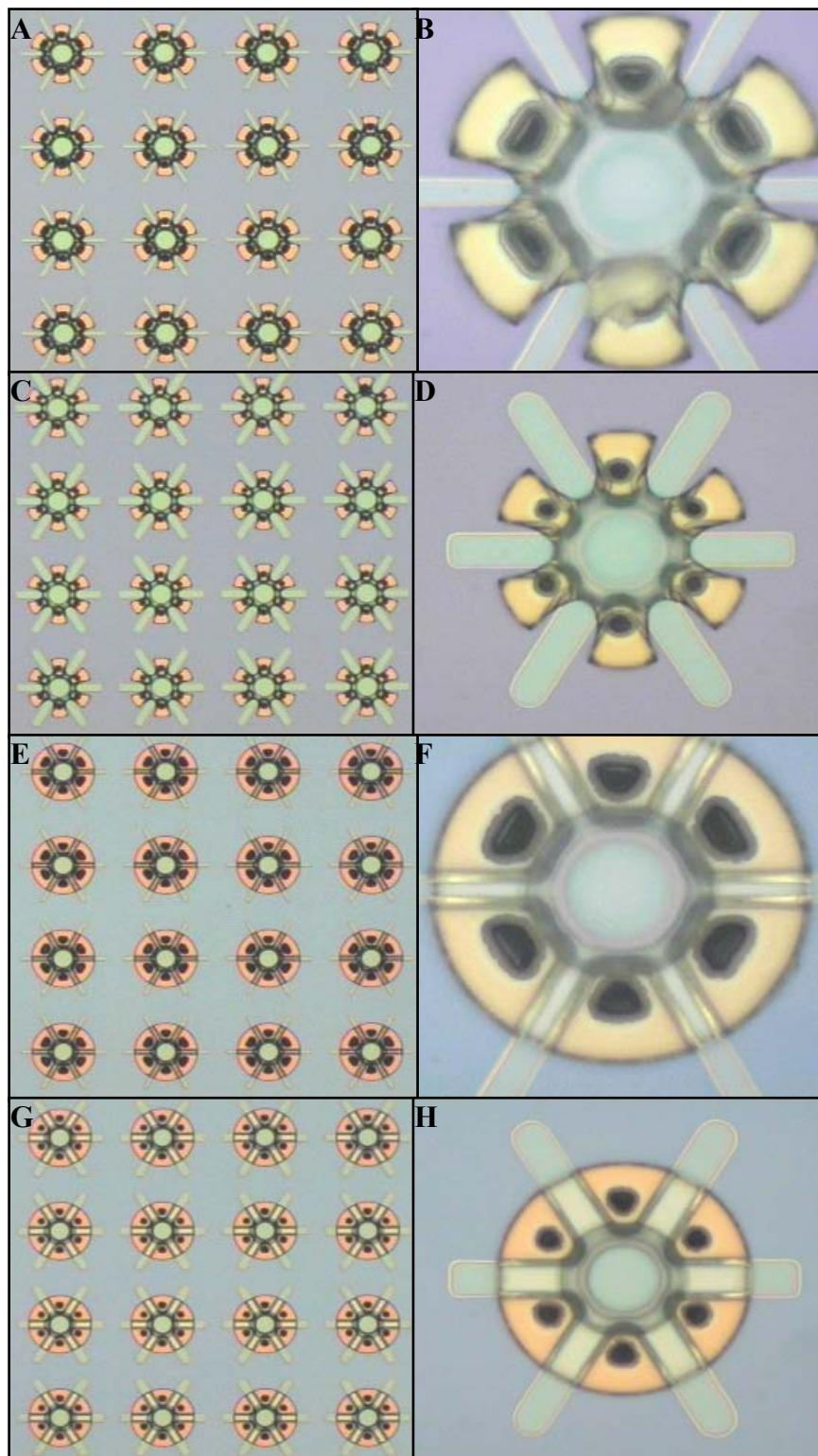

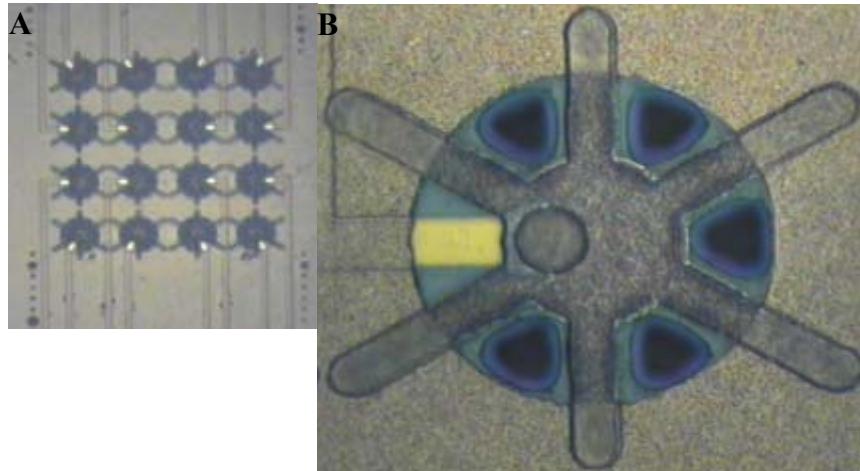

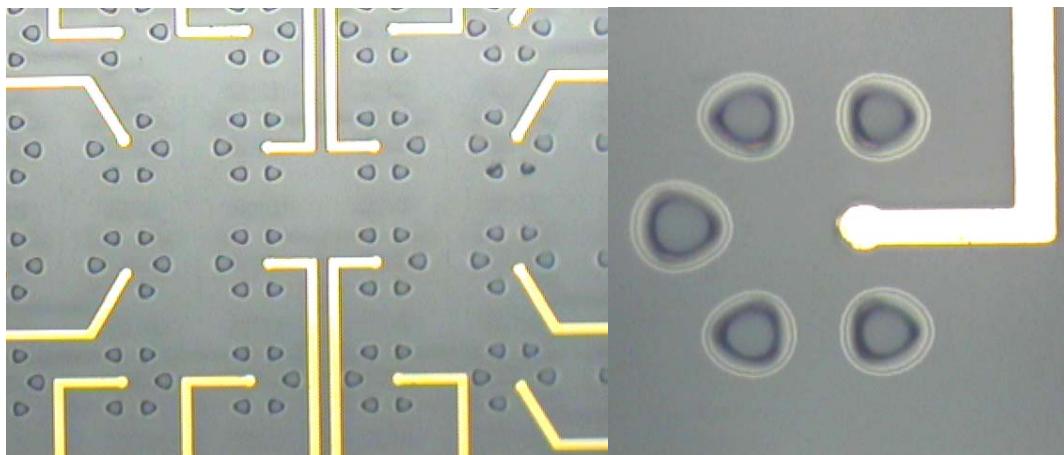

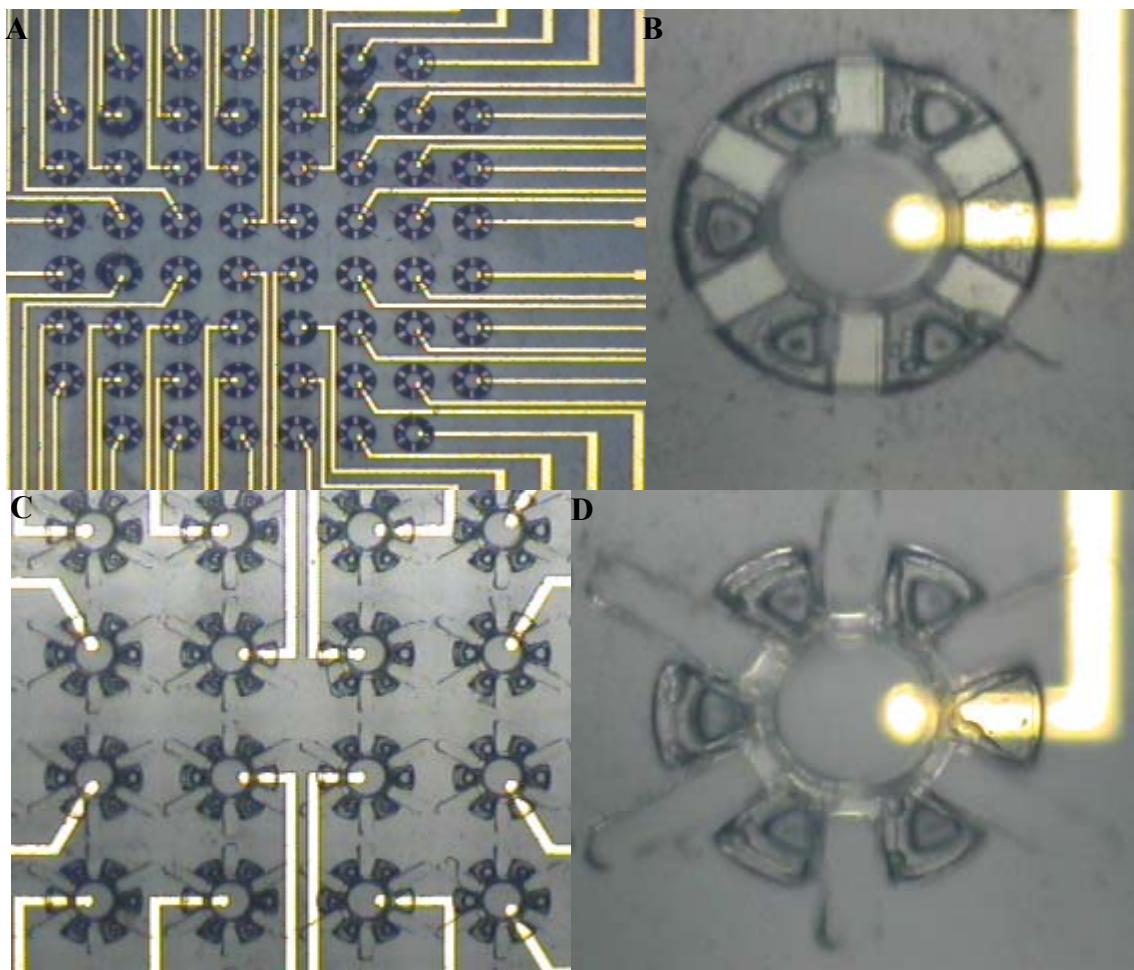

| <b>3-13.</b> Optical images of neurocage arrays and individual neurocages with soft-baked<br>photoresist tunnels and chimneys.....                   | <b>46</b> |

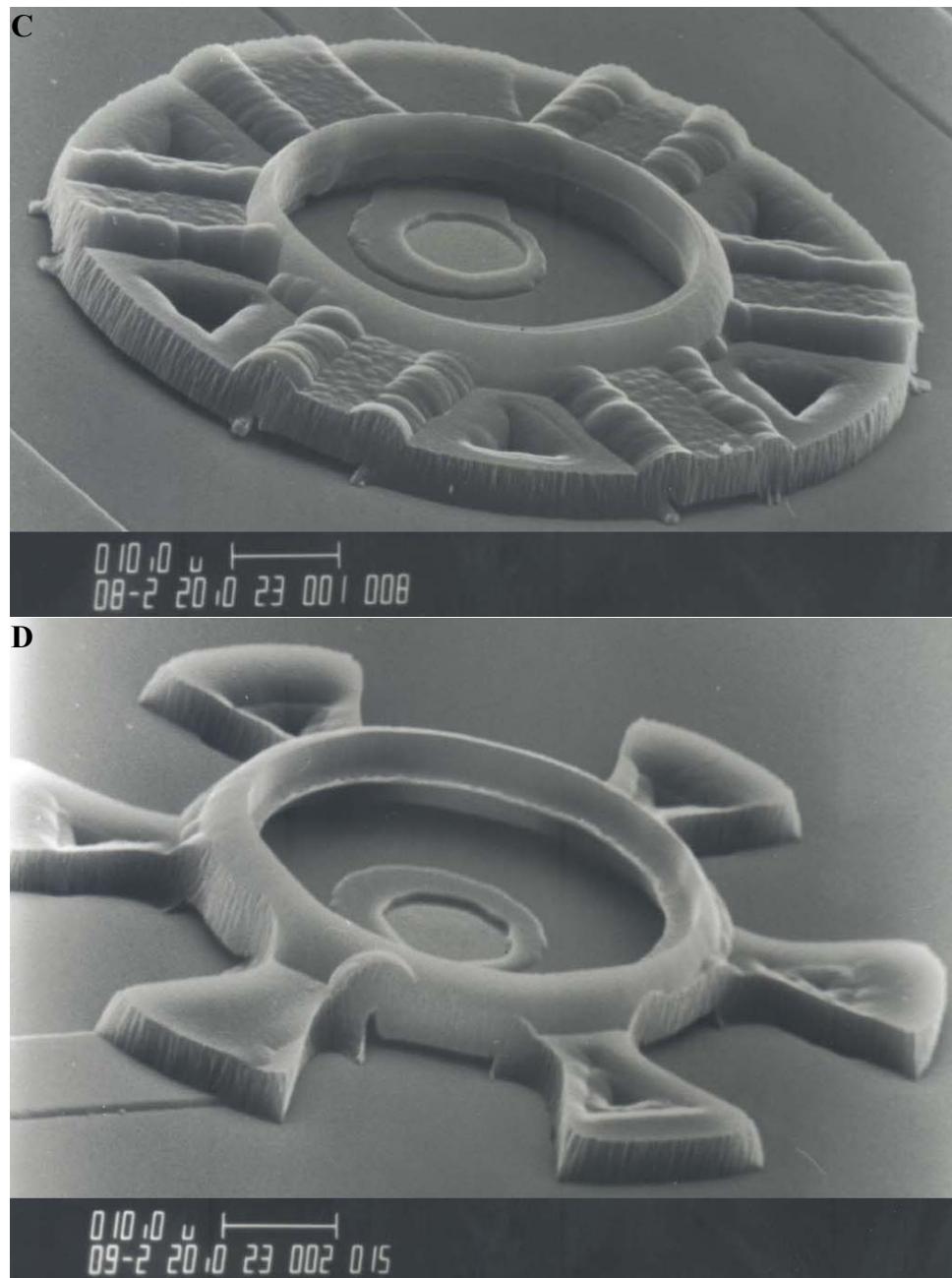

| <b>3-14.</b> SEMs of neurocages with 4 $\mu\text{m}$ long tunnels fabricated with soft-baked photoresist<br>tunnels and chimneys.....                | <b>47</b> |

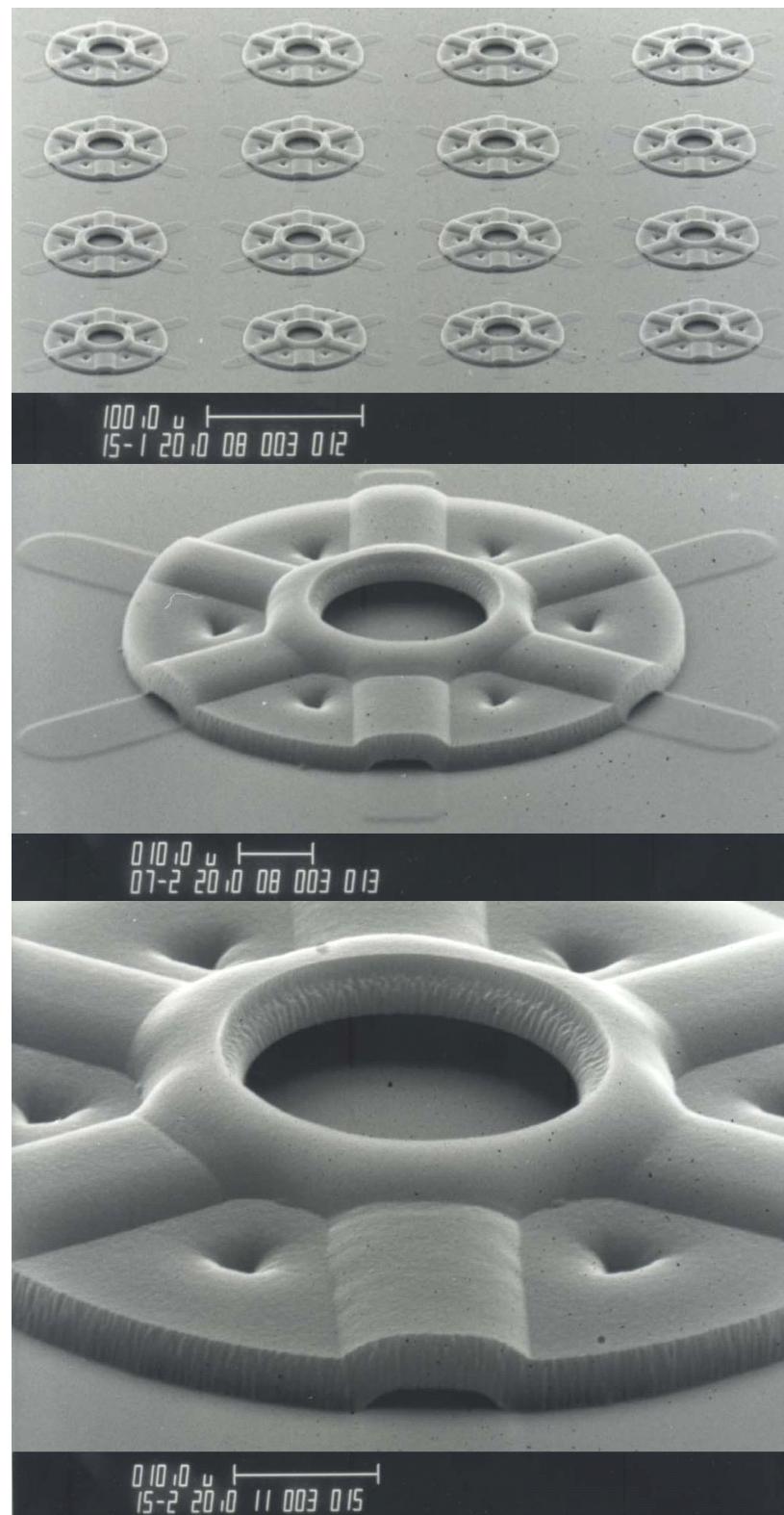

| <b>3-15.</b> SEMs of neurocages with 25 $\mu\text{m}$ long tunnels fabricated with soft-baked<br>photoresist tunnels and chimneys.....               | <b>48</b> |

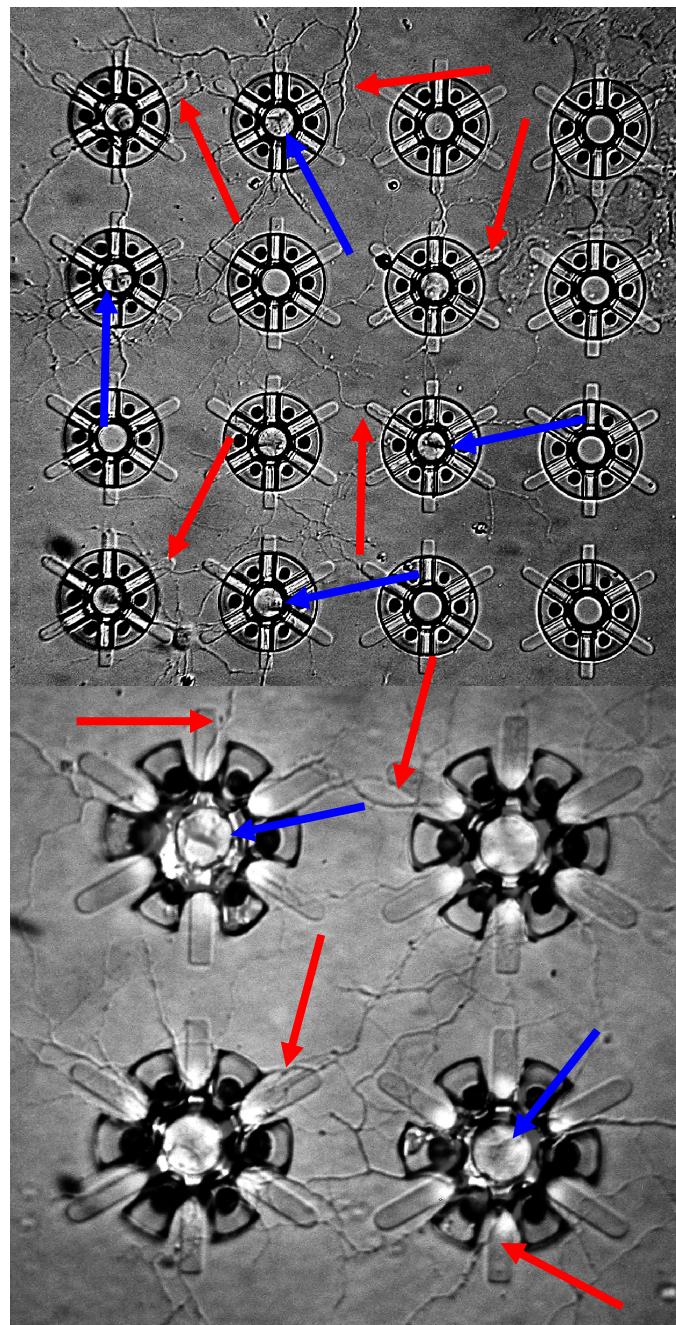

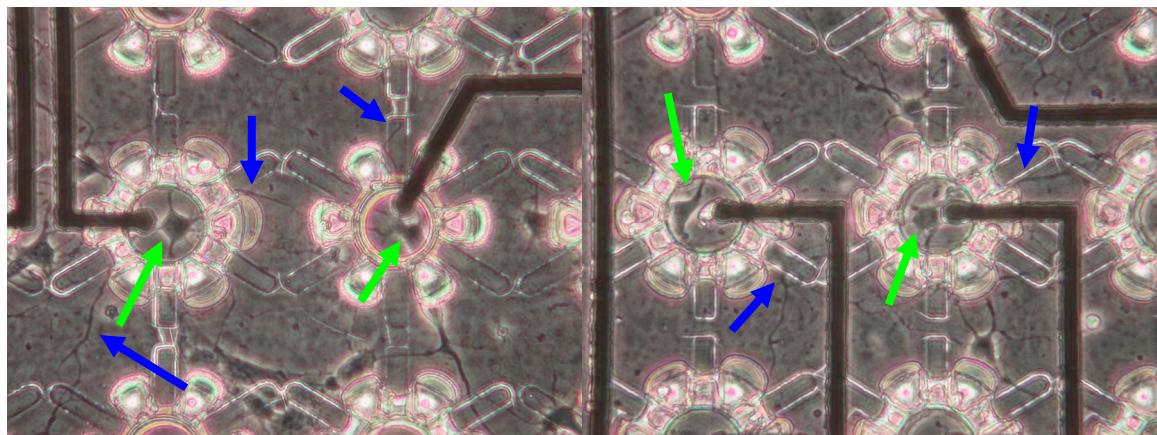

| <b>3-16.</b> Nomarski images of growing neuronal cultures.....                                                                                       | <b>50</b> |

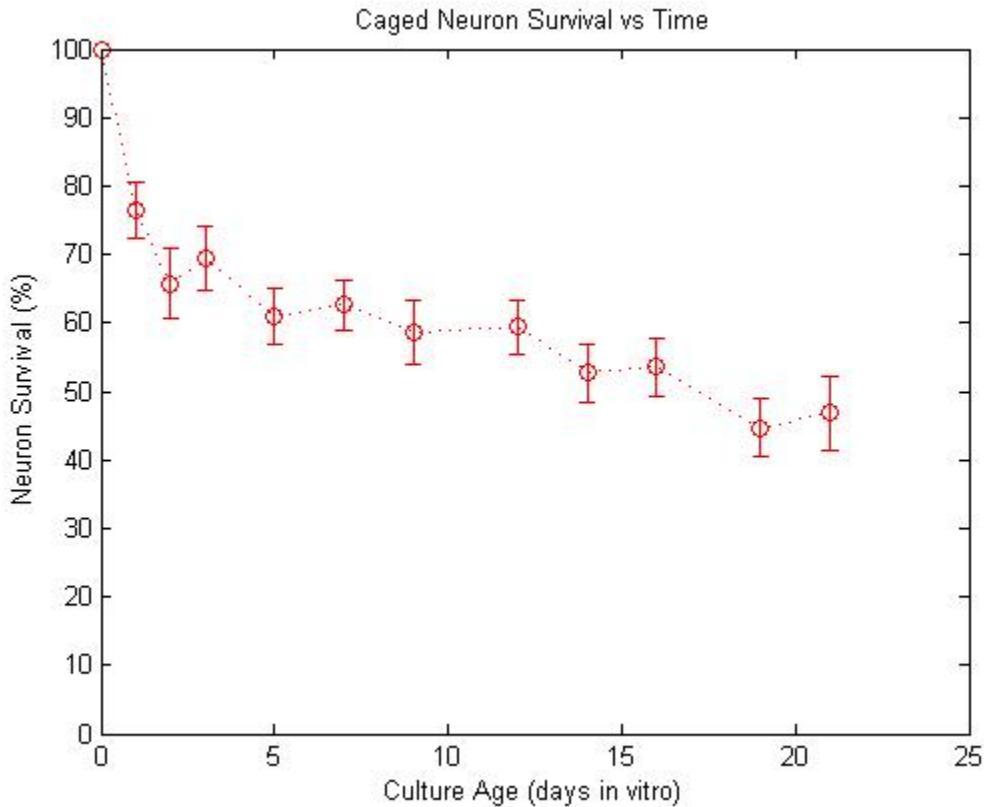

| <b>3-17.</b> Survival statistics for neurons in neurocages.....                                                                                      | <b>51</b> |

| <b>3-18.</b> Optical images of an array of neurocages after culturing and then after the<br>subsequent cleaning.....                                 | <b>51</b> |

|                                                                                                                                                      |           |

| <b>4-1.</b> SEMs of neurocages with Parylene-C insulation.....                                                                                       | <b>54</b> |

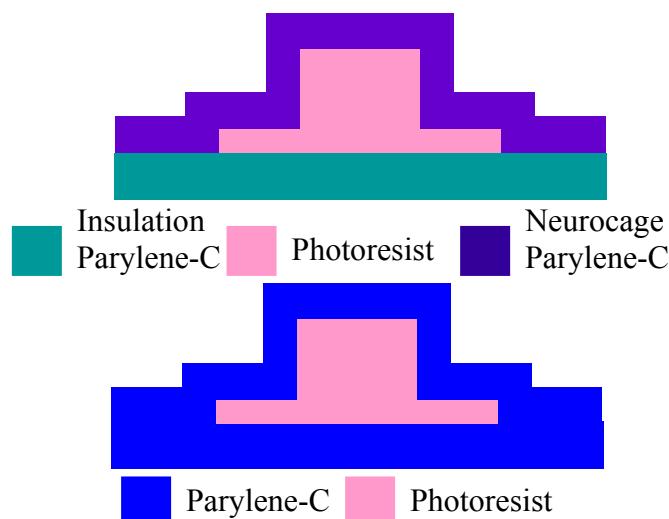

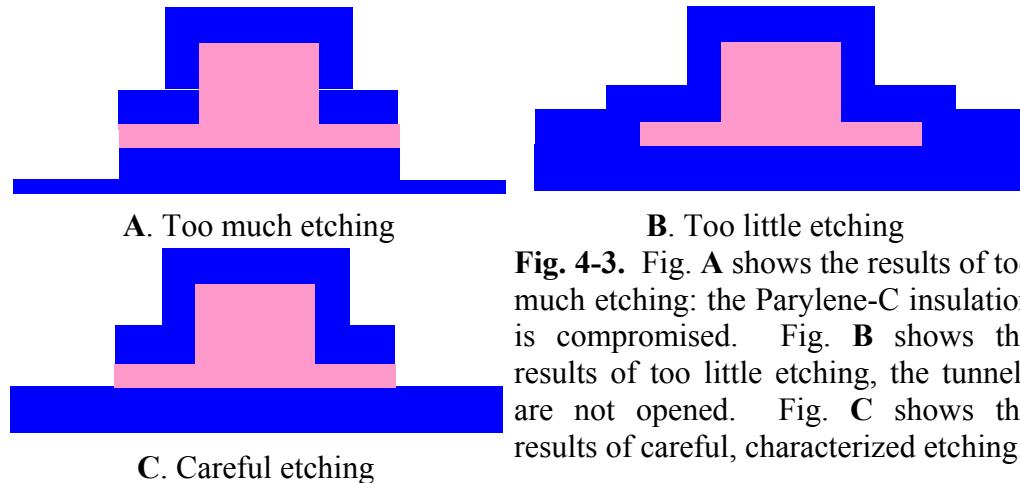

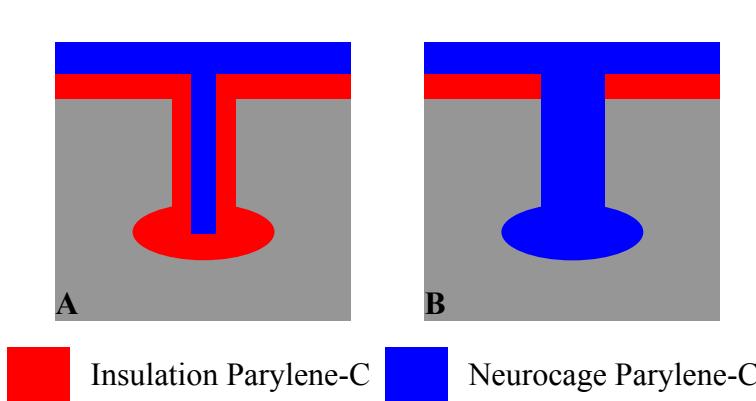

| <b>4-2.</b> Illustrates the effects of depositing the neurocage Parylene-C on top of the insulation<br>Parylene-C.....                               | <b>55</b> |

|                                                                                                                                                    |           |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>4-3.</b> Illustrates the different etching results possible when the neurocage Parylene-C is deposited on top of the insulation Parylene-C..... | <b>56</b> |

| <b>4-4.</b> Nomarski image of a growing neuron with roughened Parylene-C insulation.....                                                           | <b>57</b> |

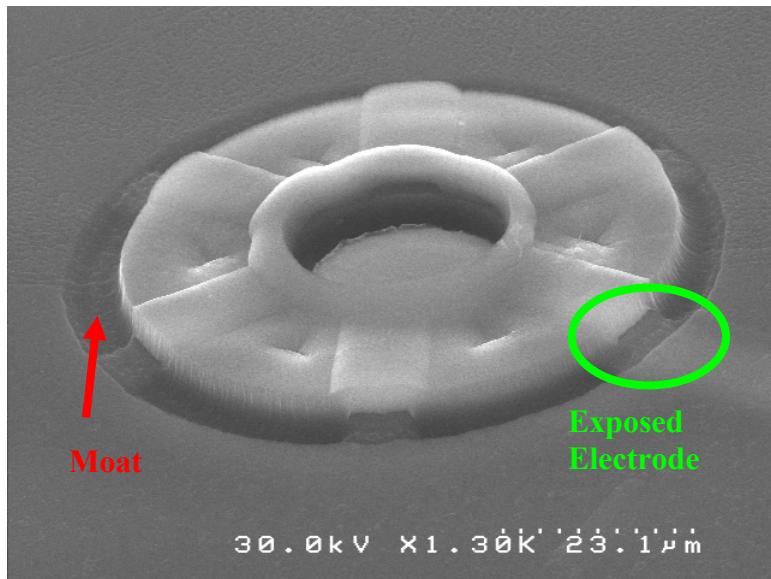

| <b>4-5.</b> SEM of a neurocage fabricated with an aluminum etch stop layer, creating moats.....                                                    | <b>59</b> |

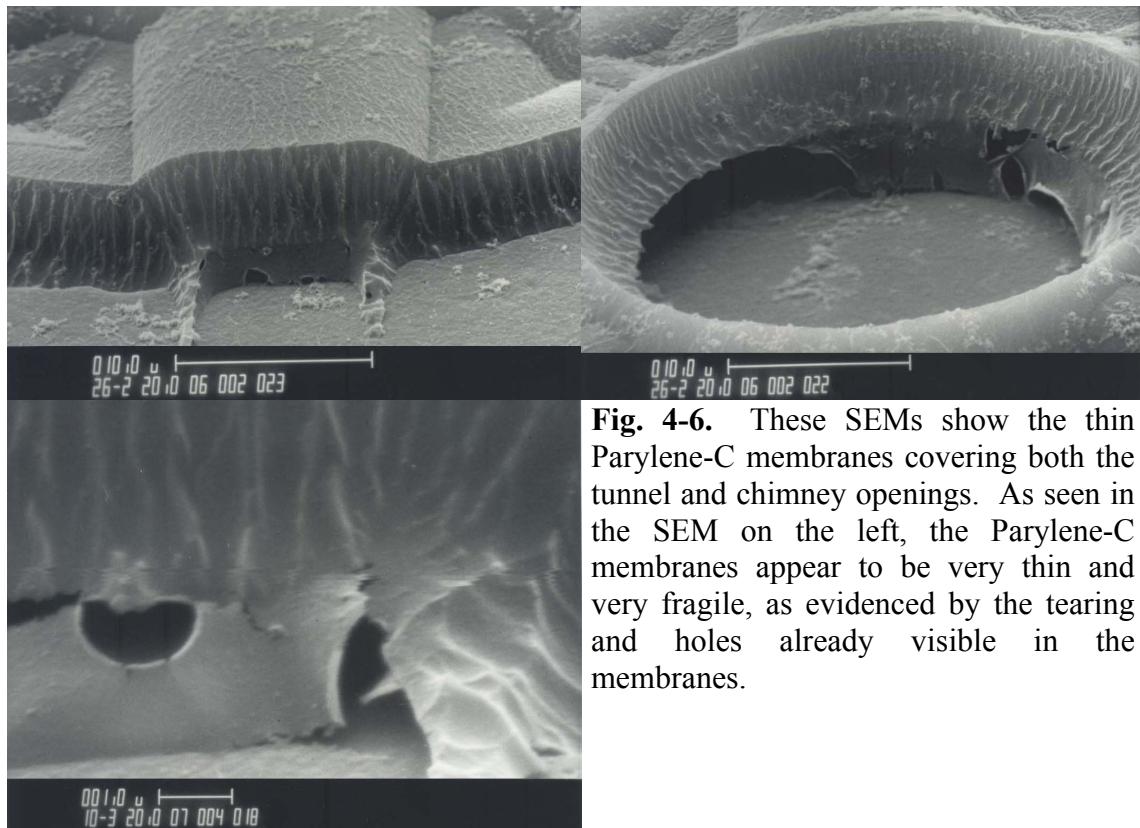

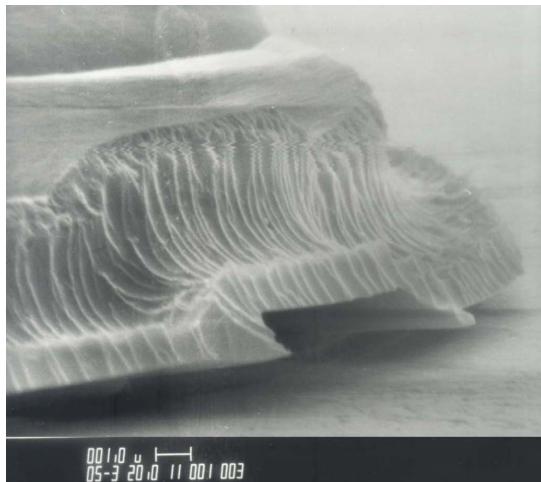

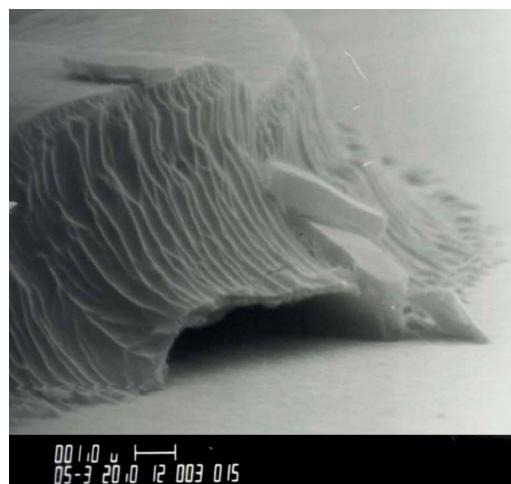

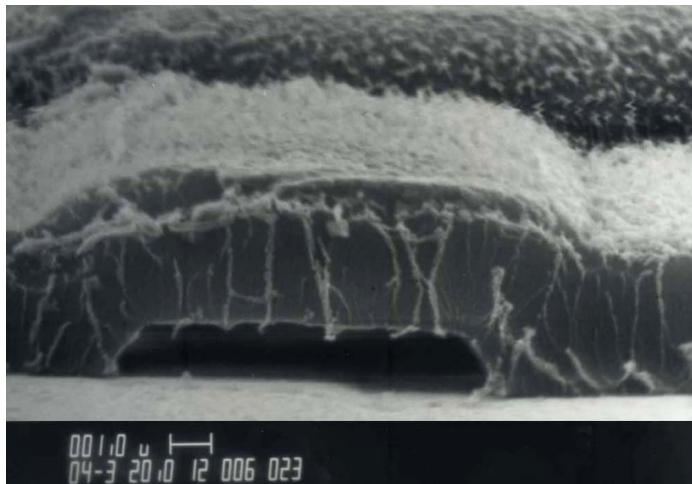

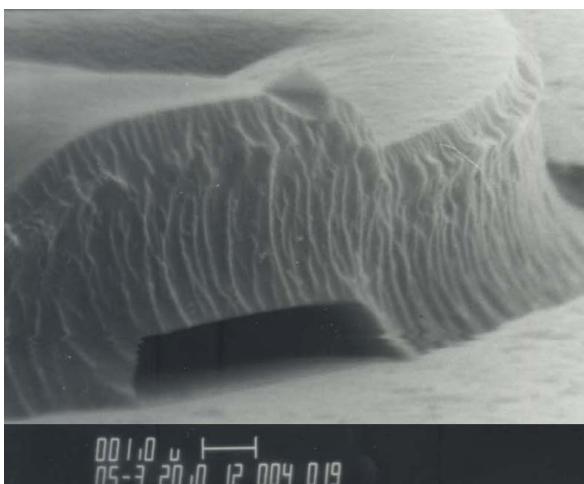

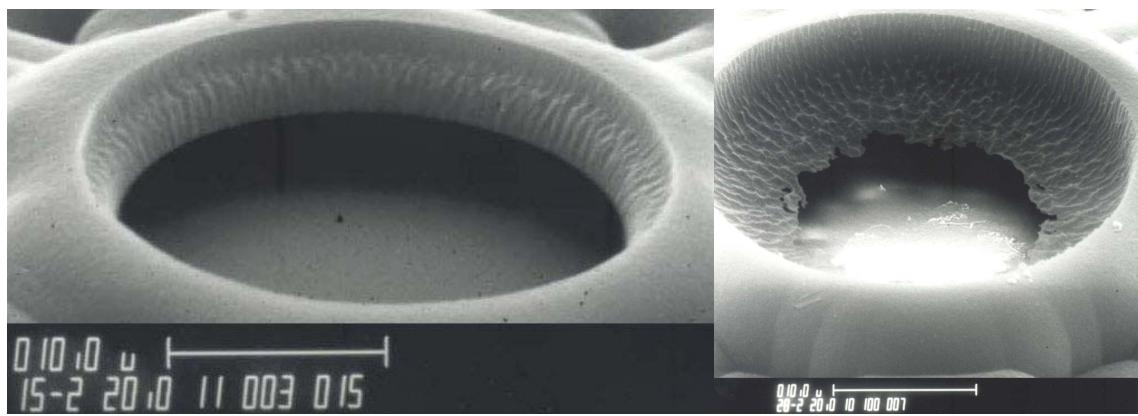

| <b>4-6.</b> SEMs of the thin Parylene-C curtains covering the tunnels and chimneys.....                                                            | <b>60</b> |

| <b>4-7.</b> SEM of a neurocage treated with dichlorobenzene to remove the curtains.....                                                            | <b>61</b> |

| <b>4-8.</b> SEM of a neurocage treated with chromic acid to remove the curtains.....                                                               | <b>61</b> |

| <b>4-9.</b> SEM of a neurocage treated with O <sub>2</sub> plasma to remove the curtains.....                                                      | <b>62</b> |

| <b>4-10.</b> SEM of a neurocage treated with ultrasonic agitation to remove the curtains.....                                                      | <b>62</b> |

| <b>4-11.</b> SEM of the original and melted chimneys.....                                                                                          | <b>63</b> |

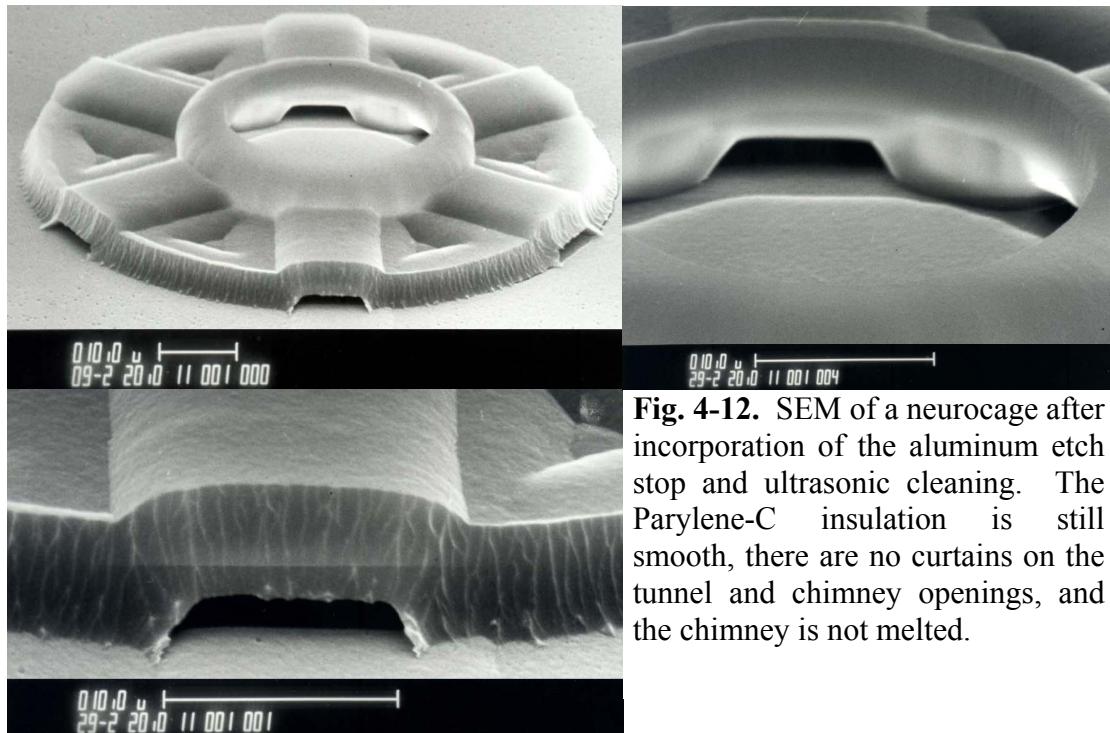

| <b>4-12.</b> SEM of a neurocage after incorporation of the aluminum etch stop and ultrasonic cleaning.....                                         | <b>64</b> |

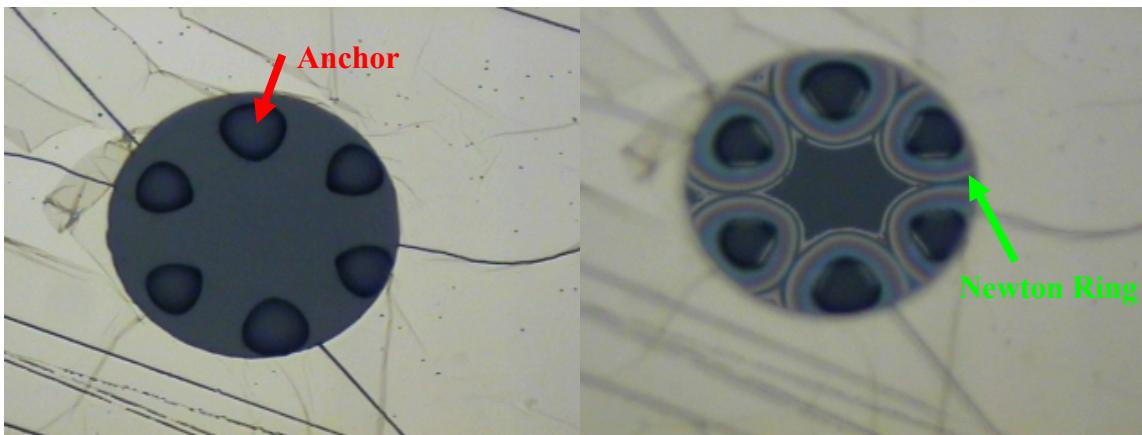

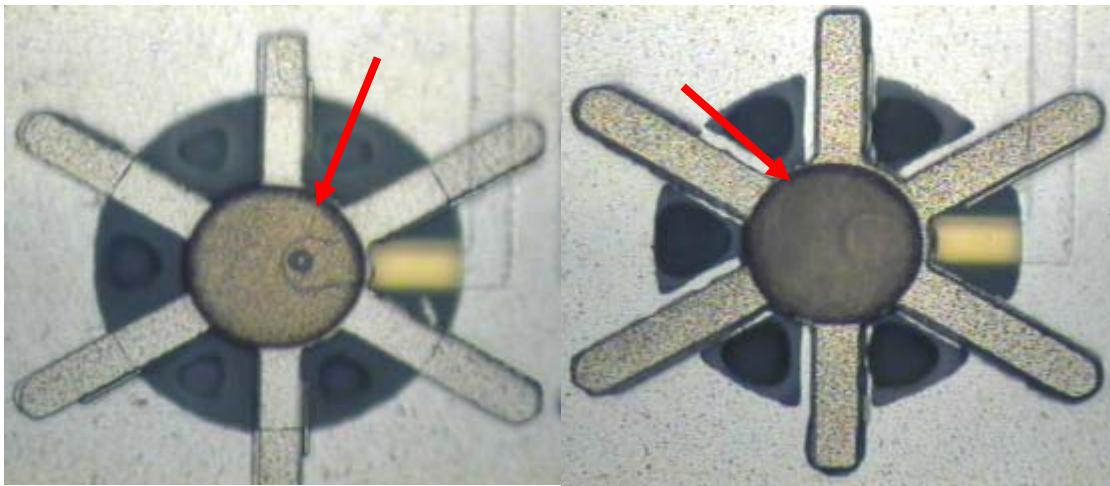

| <b>4-13.</b> Nomarksni image showing the Netwon rings indicating the Parylene-C insulation is delaminating from the oxide surface.....             | <b>65</b> |

| <b>4-14.</b> Illustrations of a pre-filled and an ideal neurocage anchor.....                                                                      | <b>67</b> |

| <b>4-15.</b> Nomarksni image of a neuron escaping from a neurocage.....                                                                            | <b>68</b> |

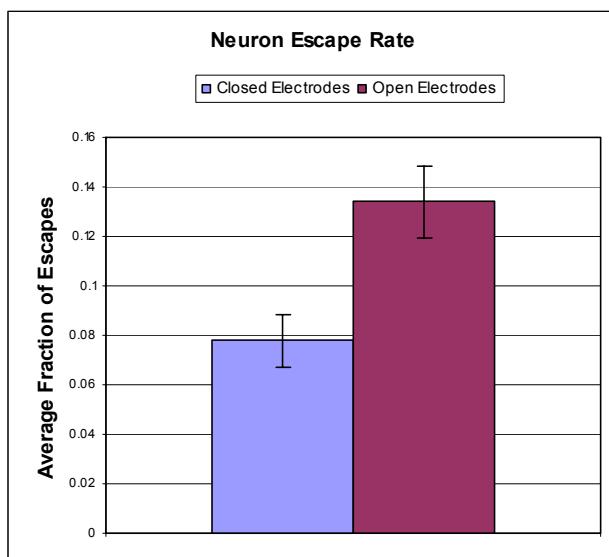

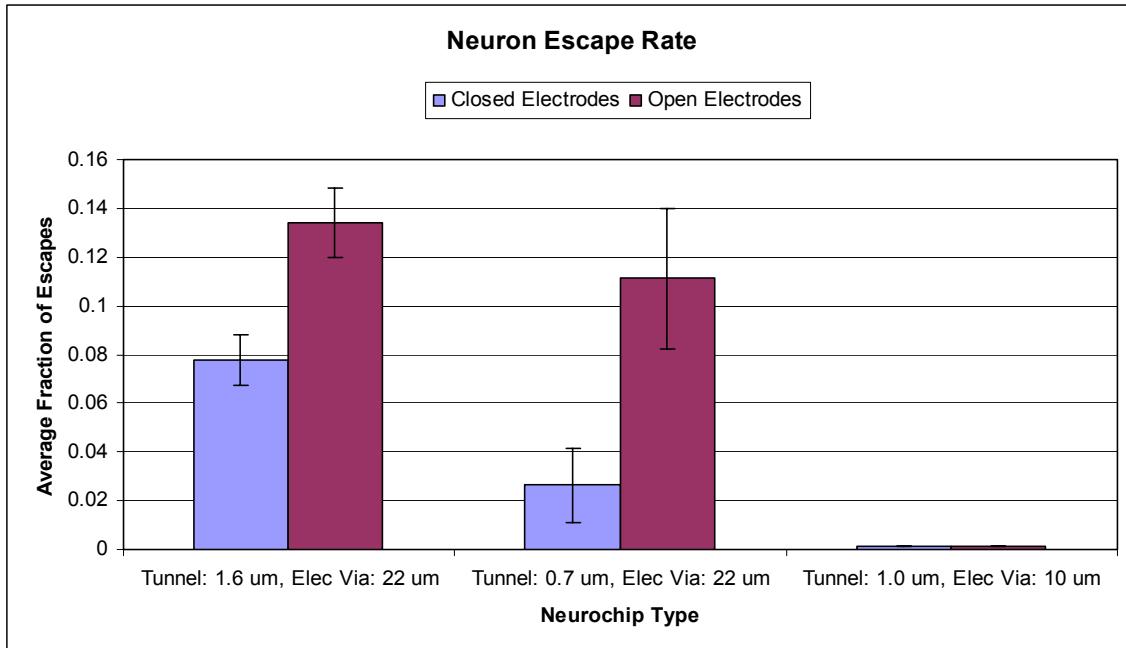

| <b>4-16.</b> Graph of the escape rate for neurons in neurocages with both open and closed electrodes.....                                          | <b>69</b> |

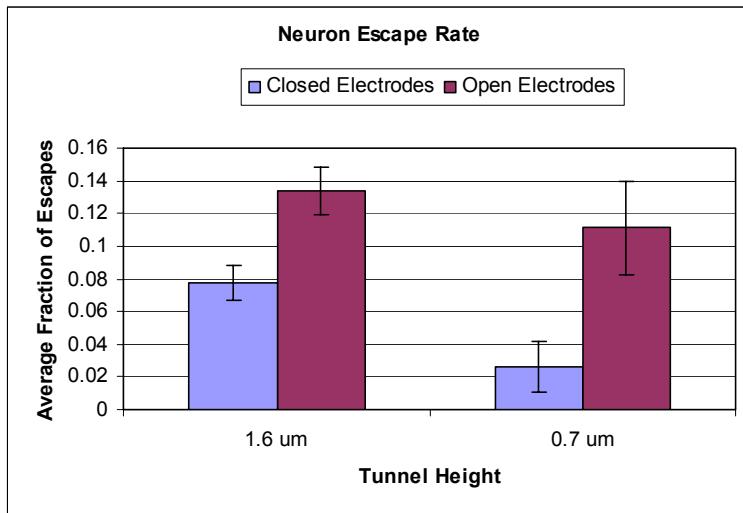

| <b>4-17.</b> Graph of the escape rate for neurons in neurocages with both open and closed electrodes and different tunnel heights.....             | <b>70</b> |

| <b>4-18.</b> Graph of the neuronal escape rate for various tunnels heights and electrode configurations.....                                       | <b>71</b> |

| <b>4-19.</b> Electrode layout for the 4 x 4 array of neurocages.....                                                                               | <b>77</b> |

|                                                                                                                                                                                                                    |           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

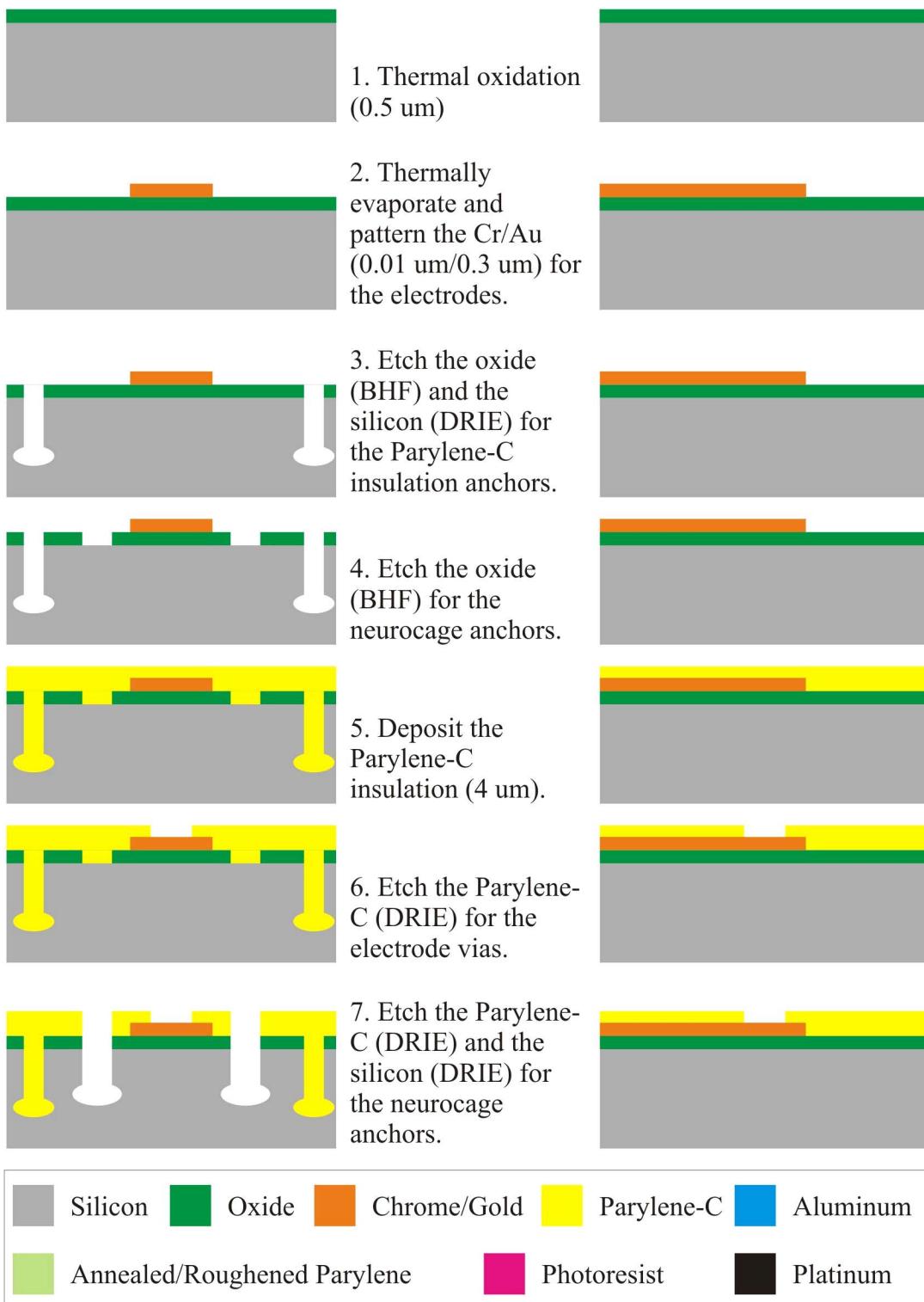

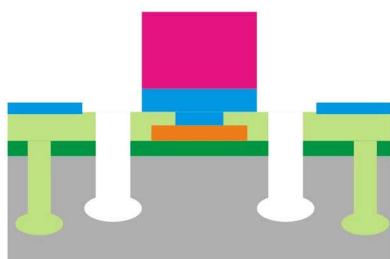

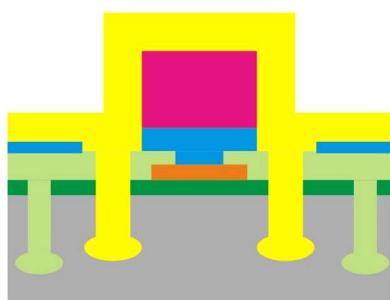

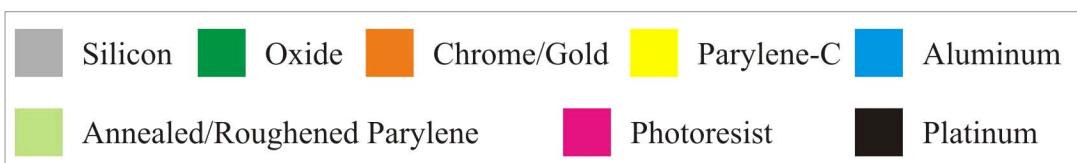

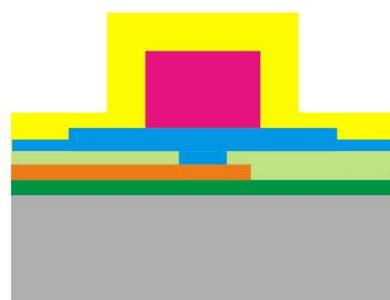

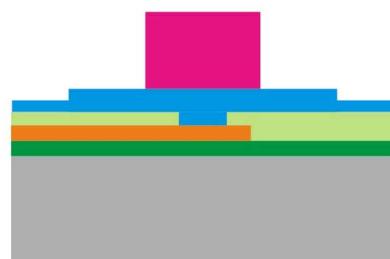

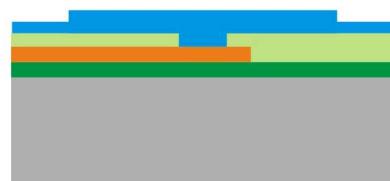

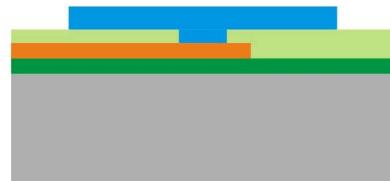

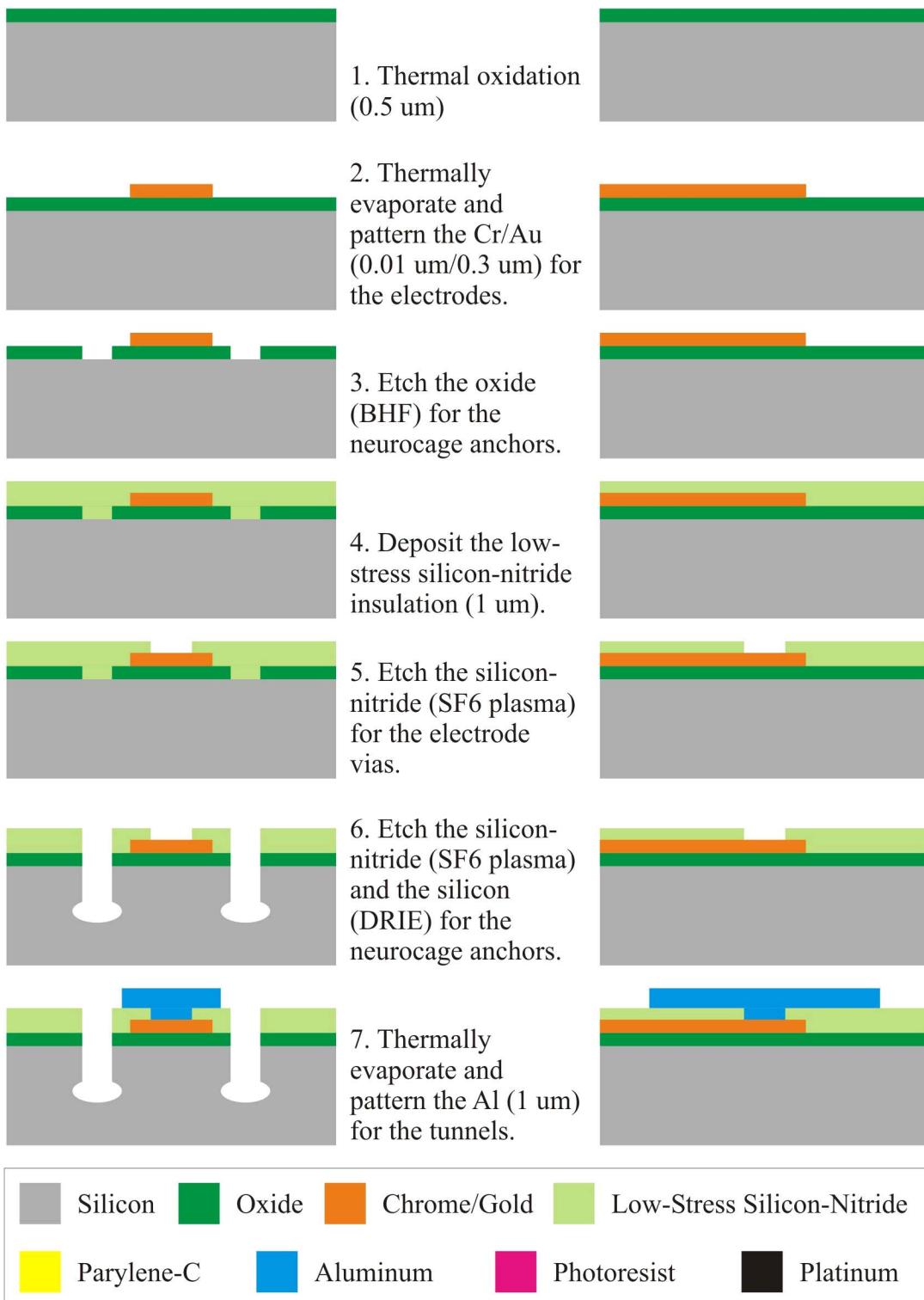

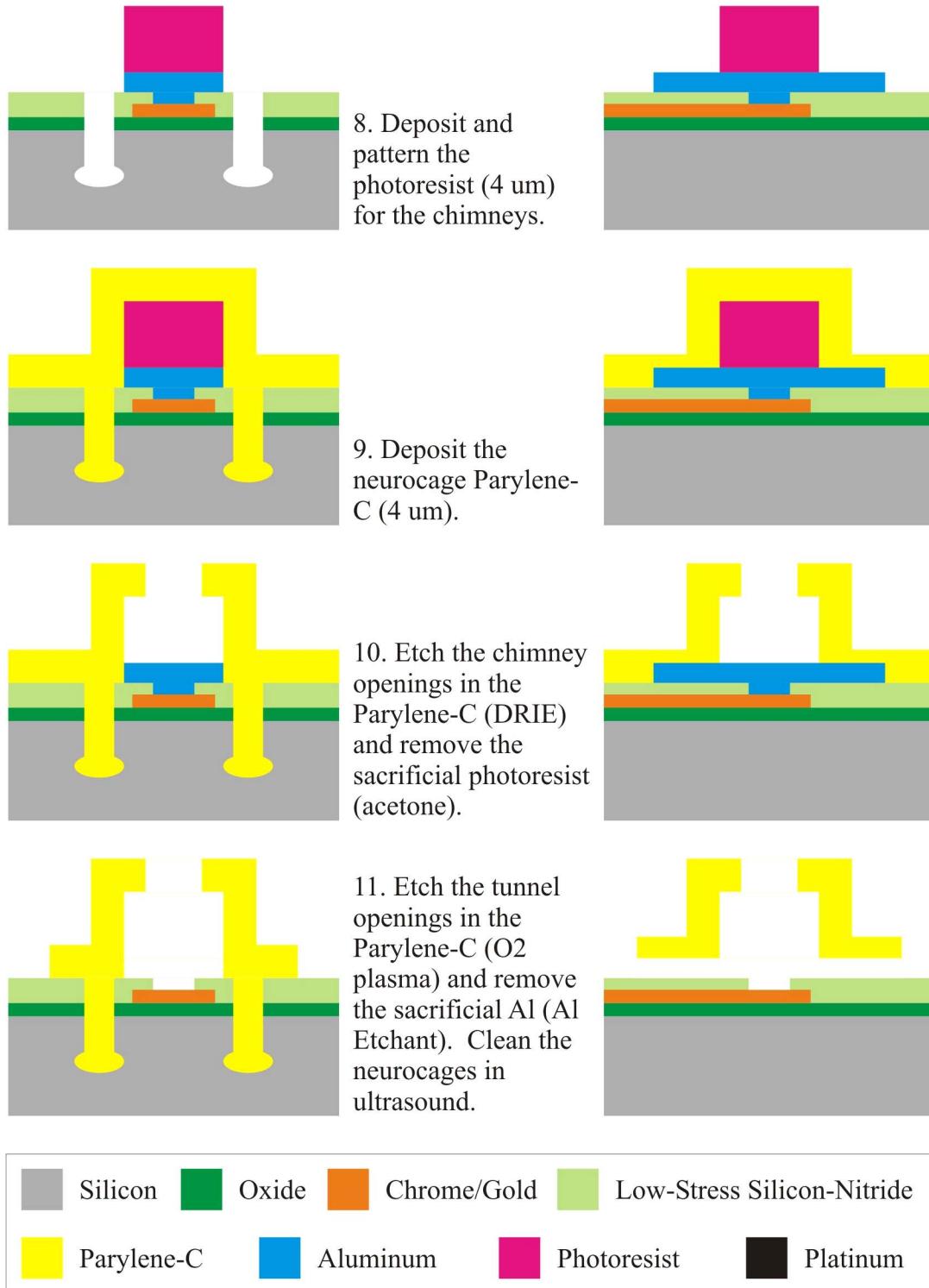

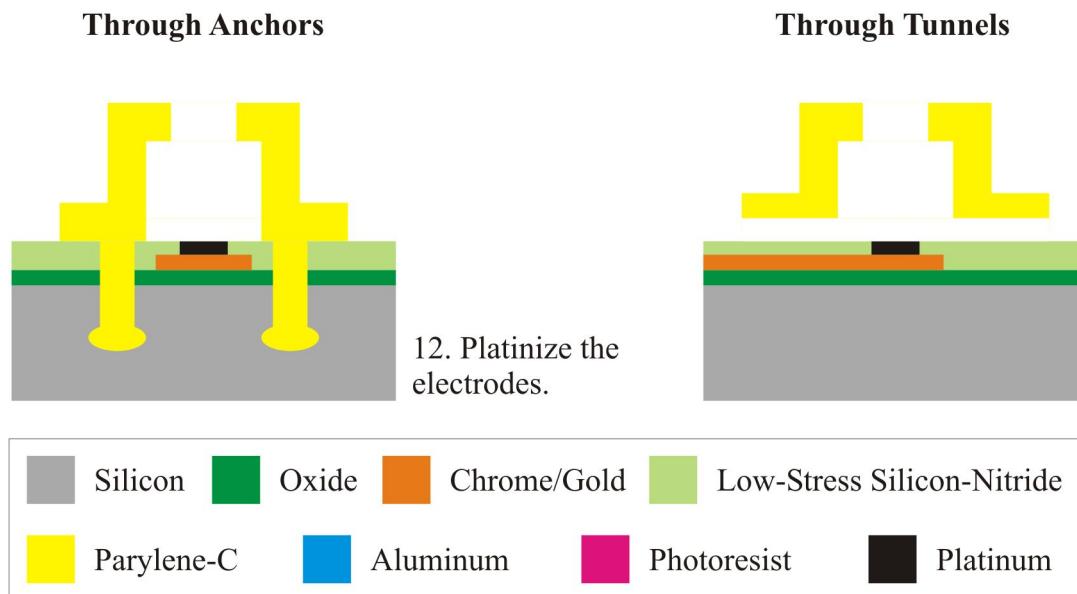

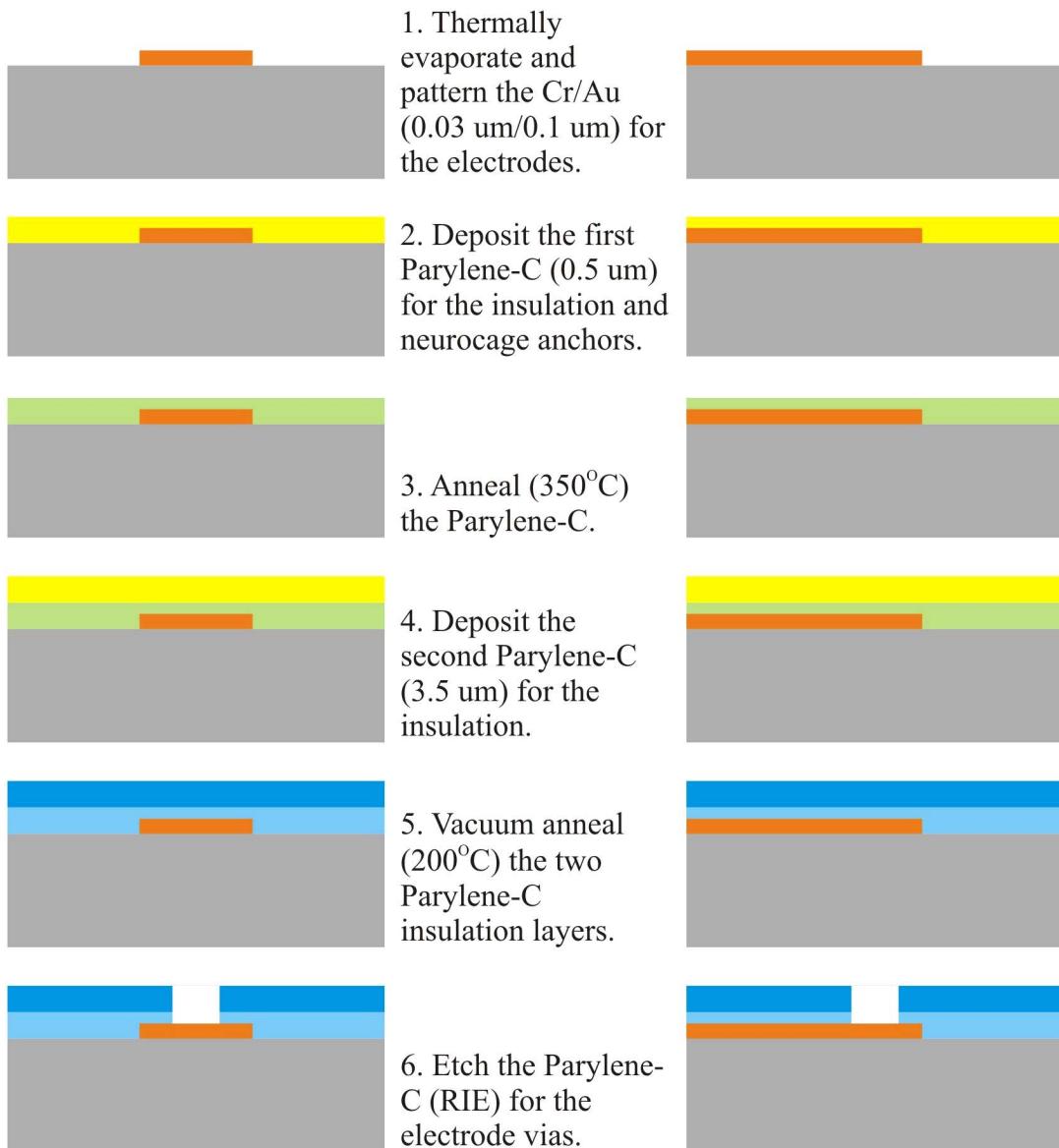

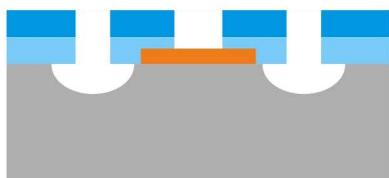

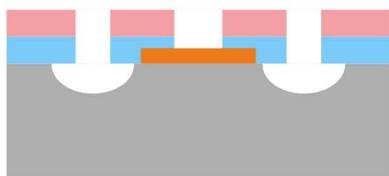

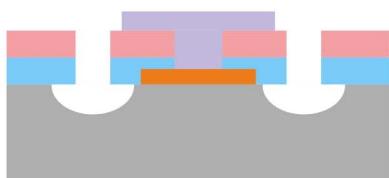

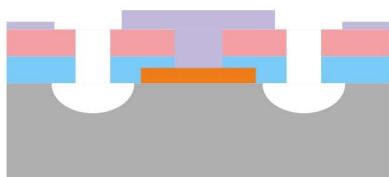

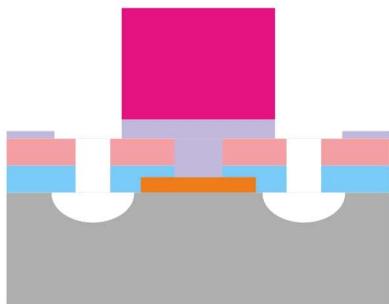

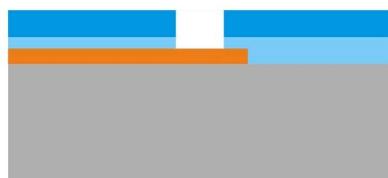

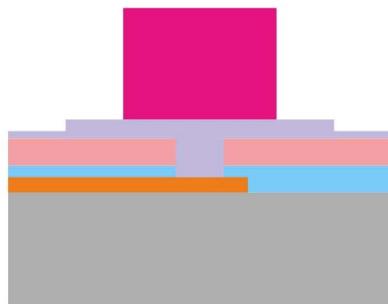

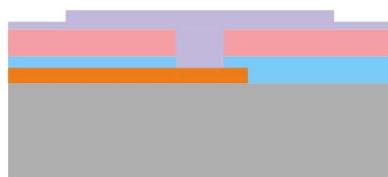

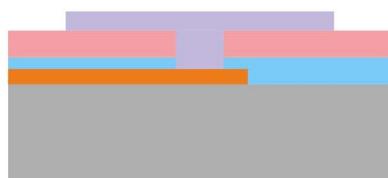

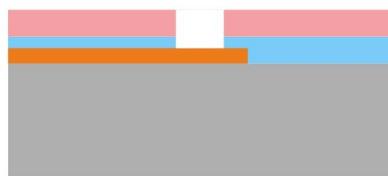

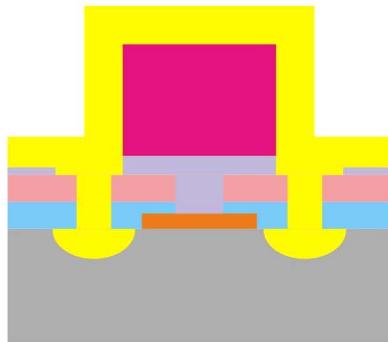

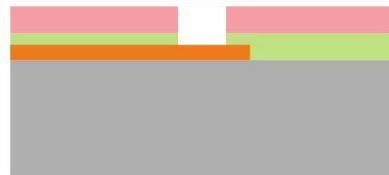

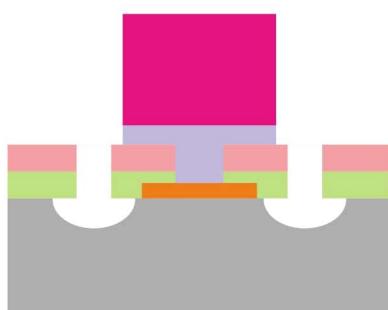

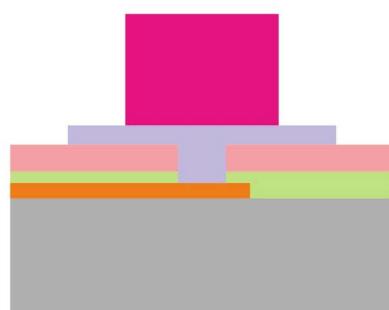

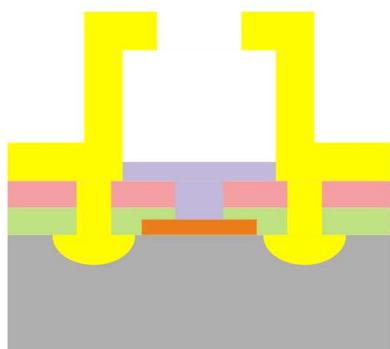

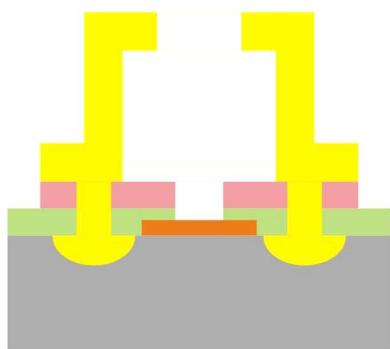

| <b>4-20.</b> Process flow for the neurocages on silicon with electrodes with Parylene-C insulation, sacrificial aluminum for the tunnels, and sacrificial soft-baked photoresist for the chimneys.....             | <b>78</b> |

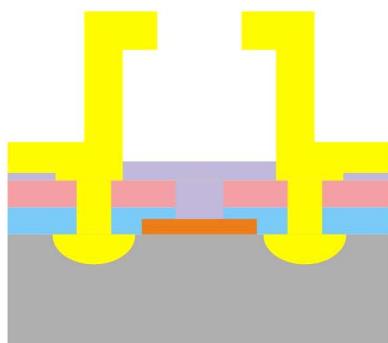

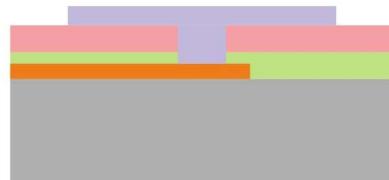

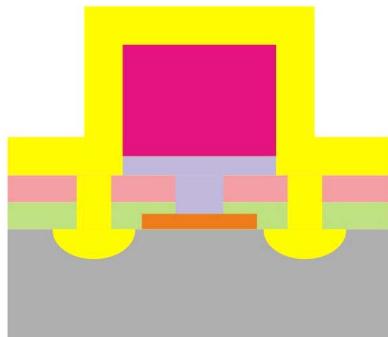

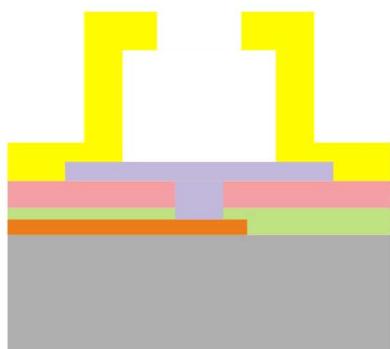

| <b>4-21.</b> Process flow for the neurocages on silicon with electrodes, low-stress silicon-nitride insulation, sacrificial aluminum for the tunnels, and sacrificial soft-baked photoresist for the chimneys..... | <b>81</b> |

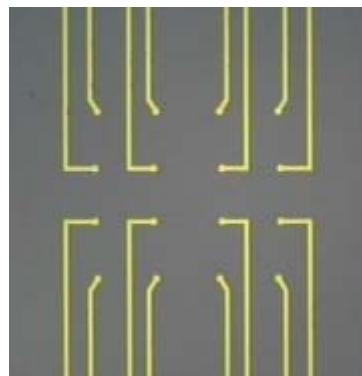

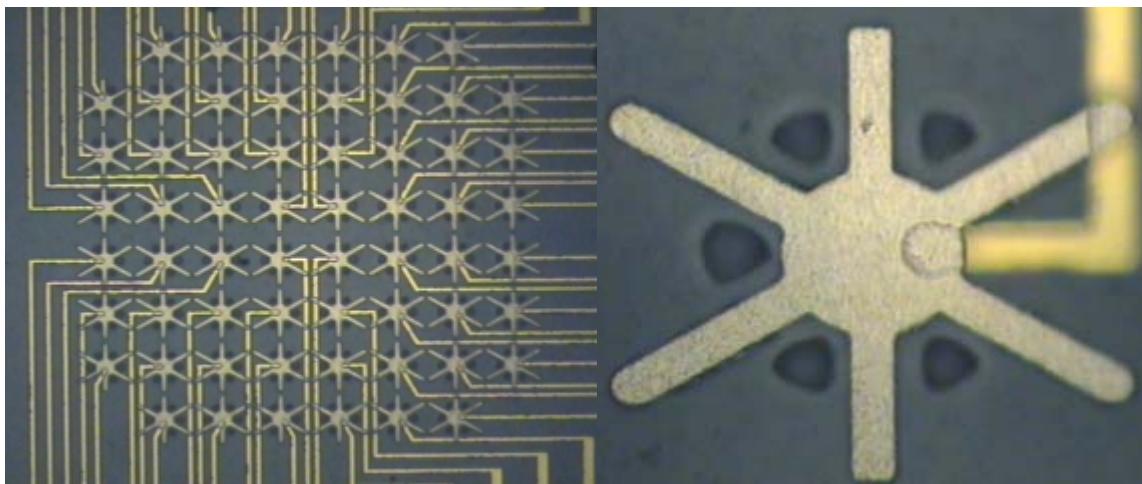

| <b>4-22.</b> Optical image of the chrome/gold electrodes.....                                                                                                                                                      | <b>84</b> |

| <b>4-23.</b> Optical image of the neurocage anchors after etching into the oxide.....                                                                                                                              | <b>85</b> |

| <b>4-24.</b> Optical image of the electrode vias etched through the insulation.....                                                                                                                                | <b>86</b> |

| <b>4-25.</b> Optical images of the neurocage anchors etched through the insulation and into the silicon.....                                                                                                       | <b>87</b> |

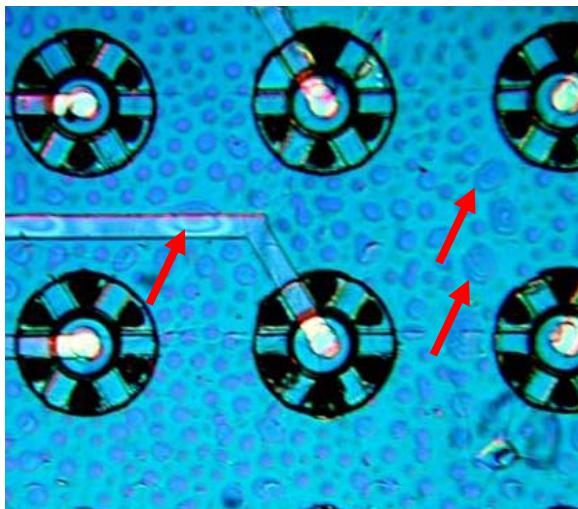

| <b>4-26.</b> Optical images of the aluminum tunnels.....                                                                                                                                                           | <b>88</b> |

| <b>4-27.</b> Optical images of the aluminum etch stop on top of the Parylene-C insulation.....                                                                                                                     | <b>88</b> |

| <b>4-28.</b> Optical image of a neurocage with a photoresist chimney.....                                                                                                                                          | <b>90</b> |

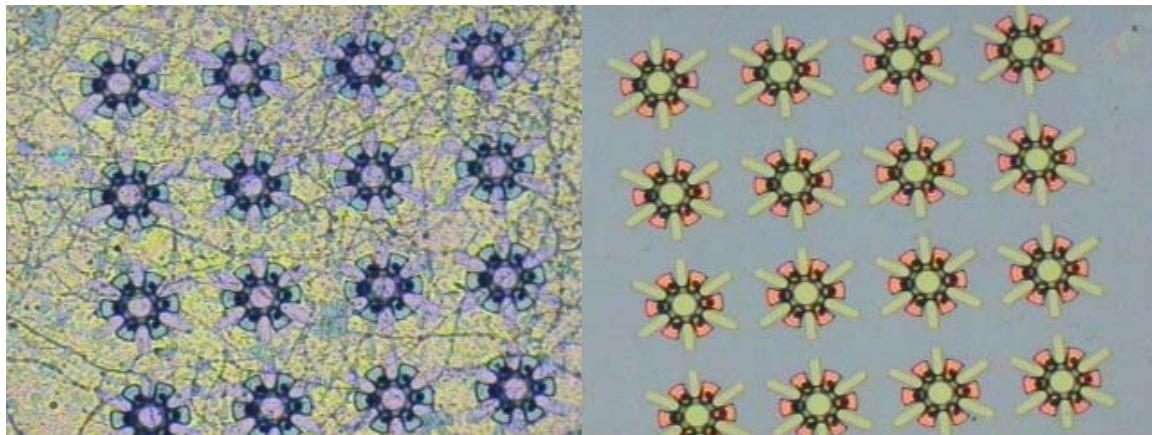

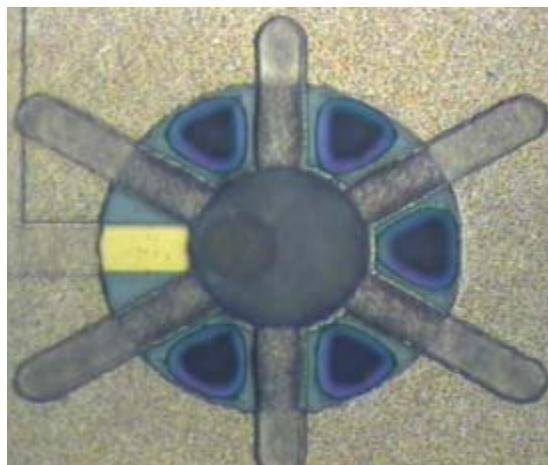

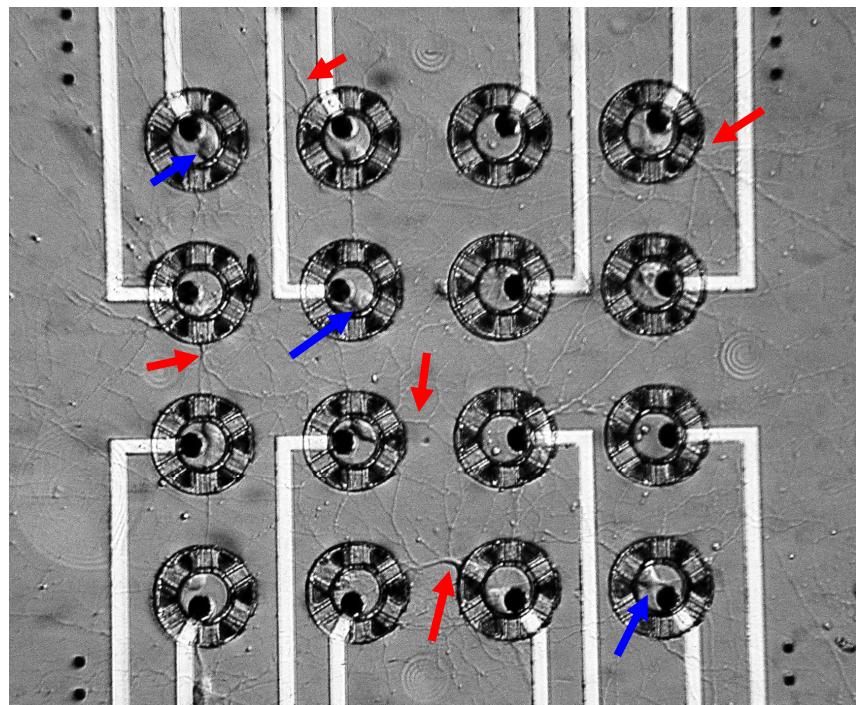

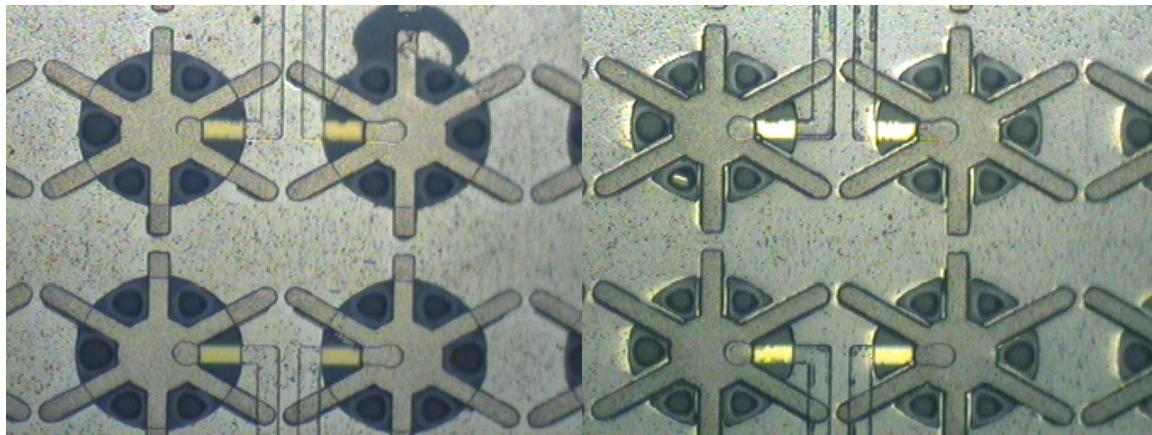

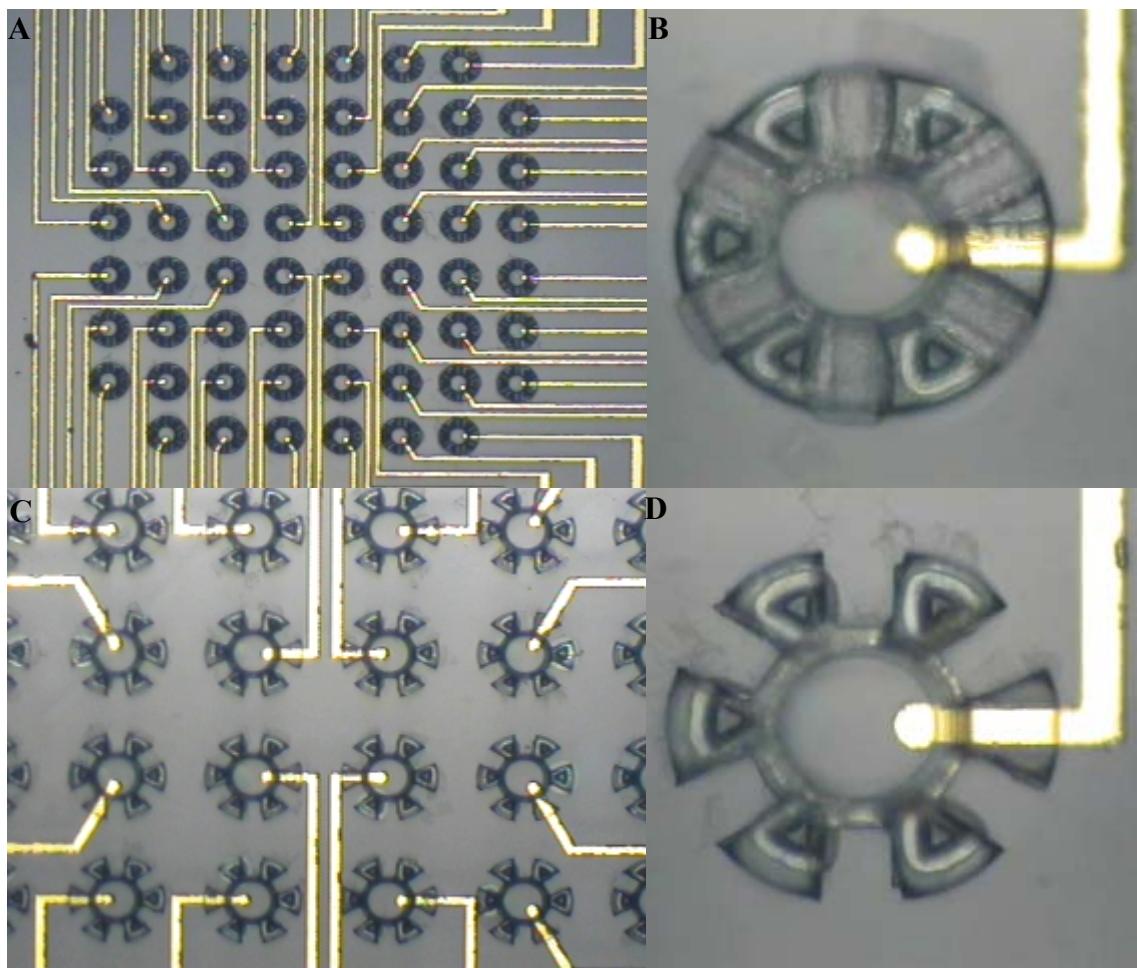

| <b>4-29.</b> Optical images of neurocages on silicon with both Parylene-C and low-stress silicon-nitride insulation and with both 25 $\mu$ m and 4 $\mu$ m long tunnels.....                                       | <b>91</b> |

| <b>4-30.</b> SEM of neurocages on silicon with both Parylene-C and low-stress silicon-nitride insulation and with both 25 $\mu$ m and 4 $\mu$ m long tunnels.....                                                  | <b>92</b> |

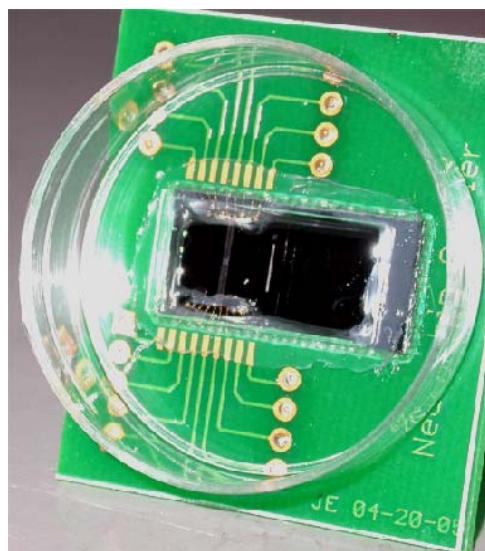

| <b>4-31.</b> Optical image of a neurochip ready for culturing.....                                                                                                                                                 | <b>94</b> |

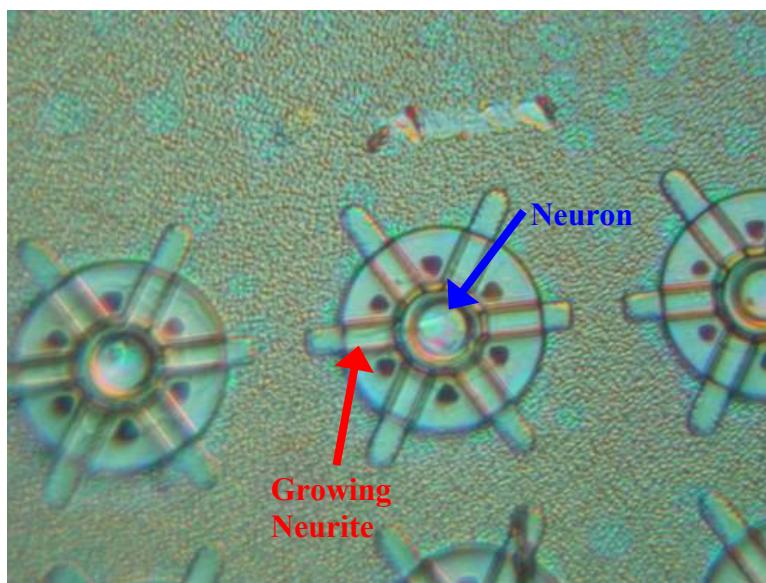

| <b>4-32.</b> Nomarski image of neurons growing in neurocages with Parylene-C insulation....                                                                                                                        | <b>95</b> |

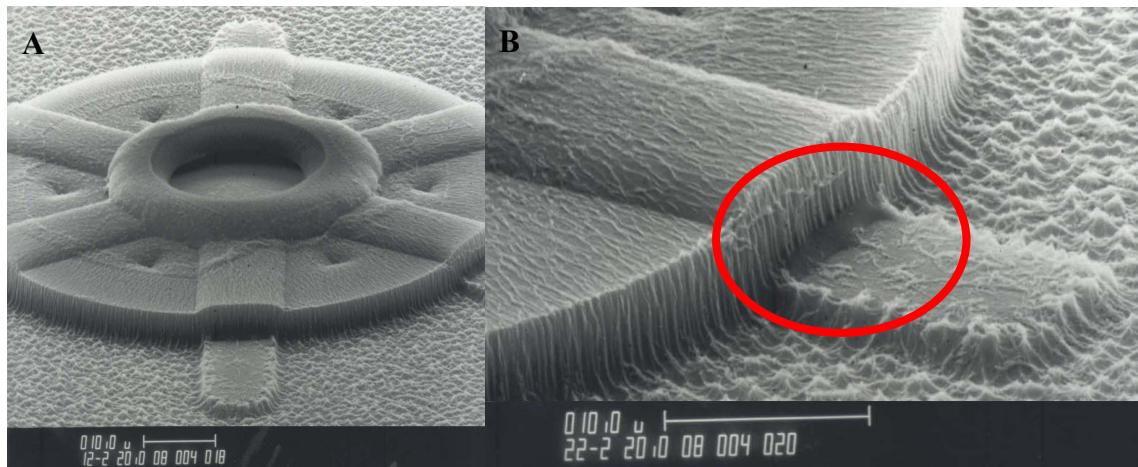

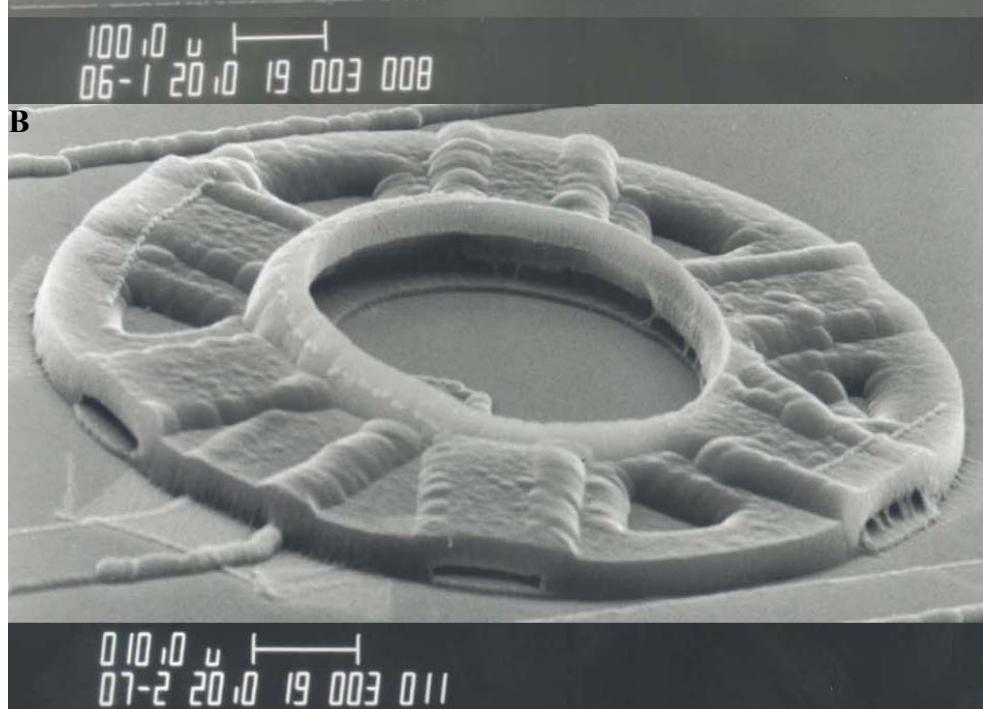

| <b>4-33.</b> SEM of a fixed neuron inside a neurocage after 8 days of growth.....                                                                                                                                  | <b>96</b> |

| <b>4-34.</b> Neuronal survival rate for neurons inside neurocages on silicon.....                                                                                                                                  | <b>97</b> |

|                                                                                                                                                                                  |            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

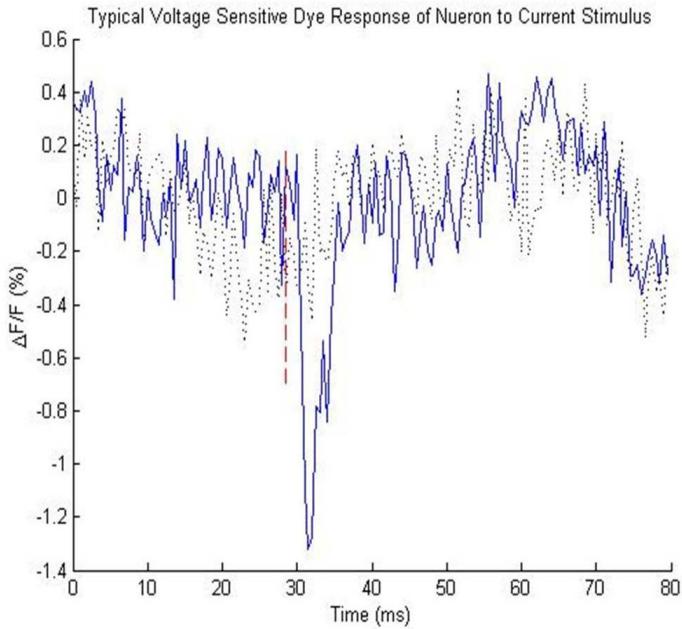

| <b>4-35.</b> Graph of the change in fluorescence intensity of the voltage sensitive dye showing the action potential response after the current stimulus.....                    | <b>98</b>  |

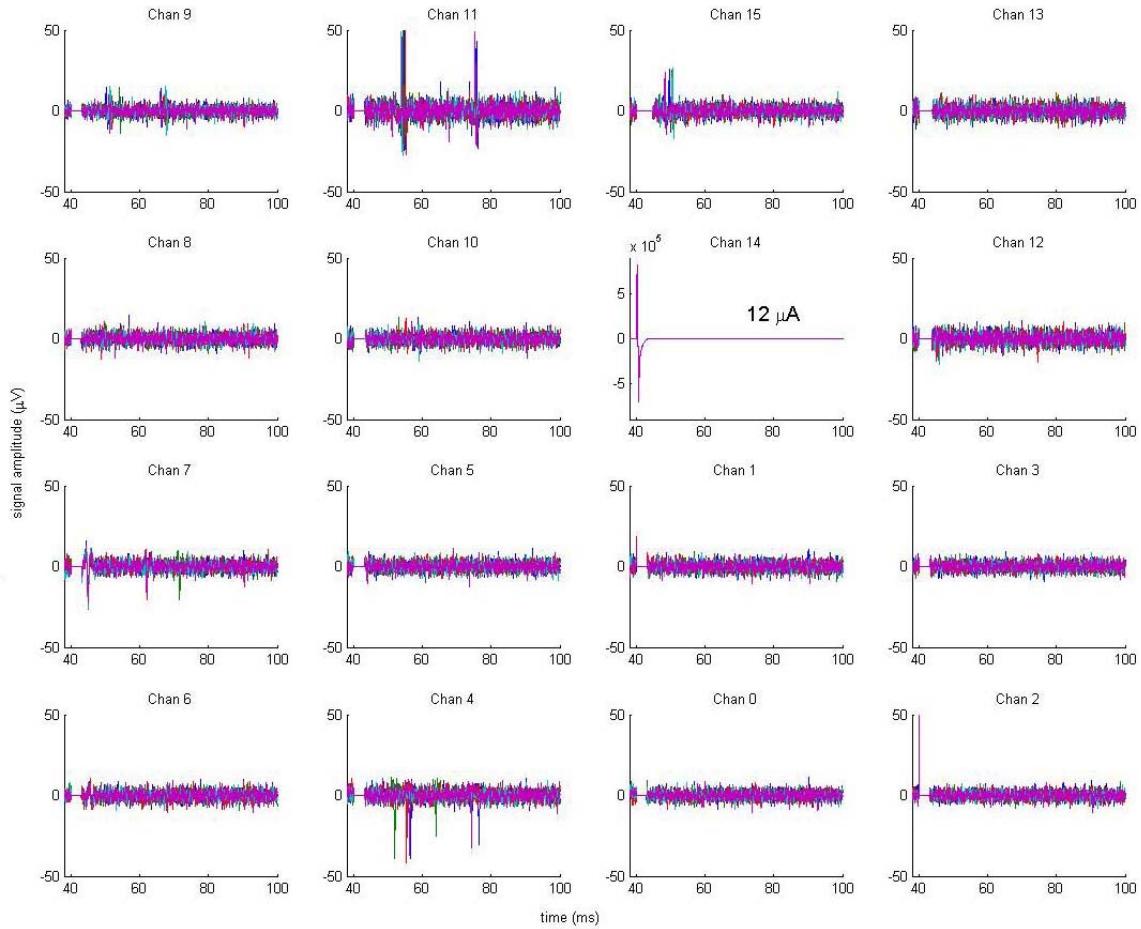

| <b>4-36.</b> Electrical recordings from neurons in the neural networks after the current stimulus.....                                                                           | <b>99</b>  |

| <b>4-37.</b> Electrical recordings of the spontaneous activity in the neural network.....                                                                                        | <b>100</b> |

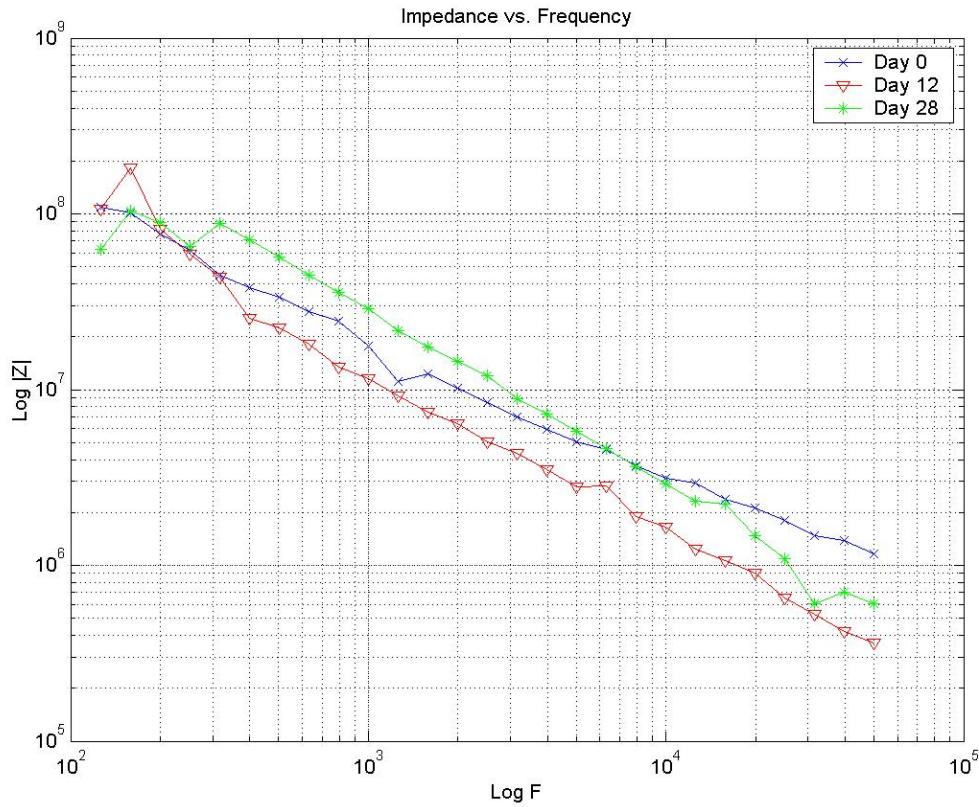

| <b>4-38.</b> Graph of the electrical impedance of the electrodes with Parylene-C insulation over time.....                                                                       | <b>102</b> |

|                                                                                                                                                                                  |            |

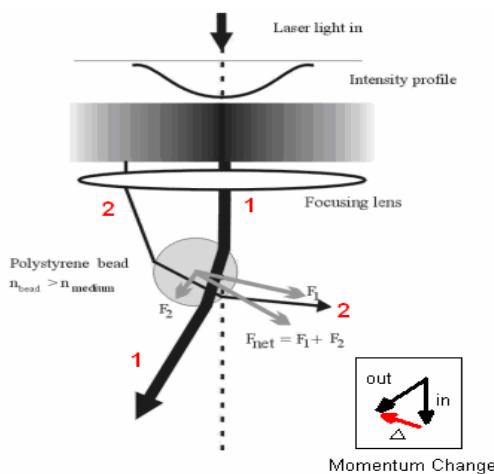

| <b>5-1.</b> Illustration of the forces applied by the laser tweezers.....                                                                                                        | <b>106</b> |

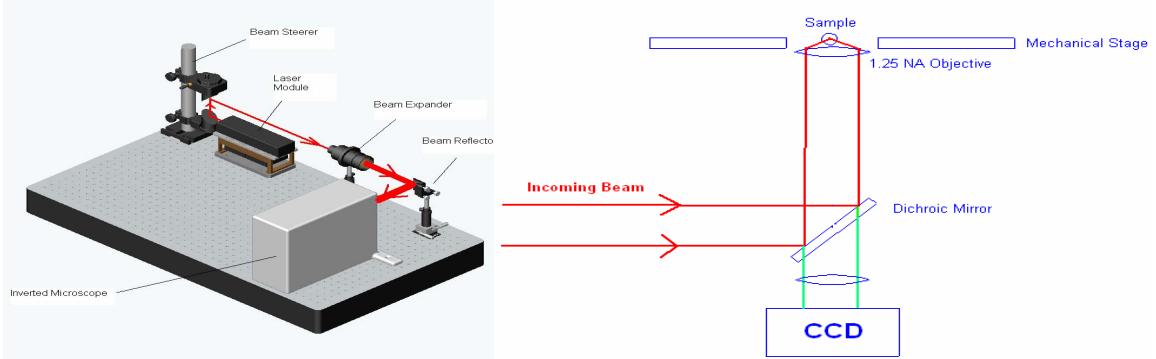

| <b>5-2.</b> Illustration of the laser tweezers setup.....                                                                                                                        | <b>107</b> |

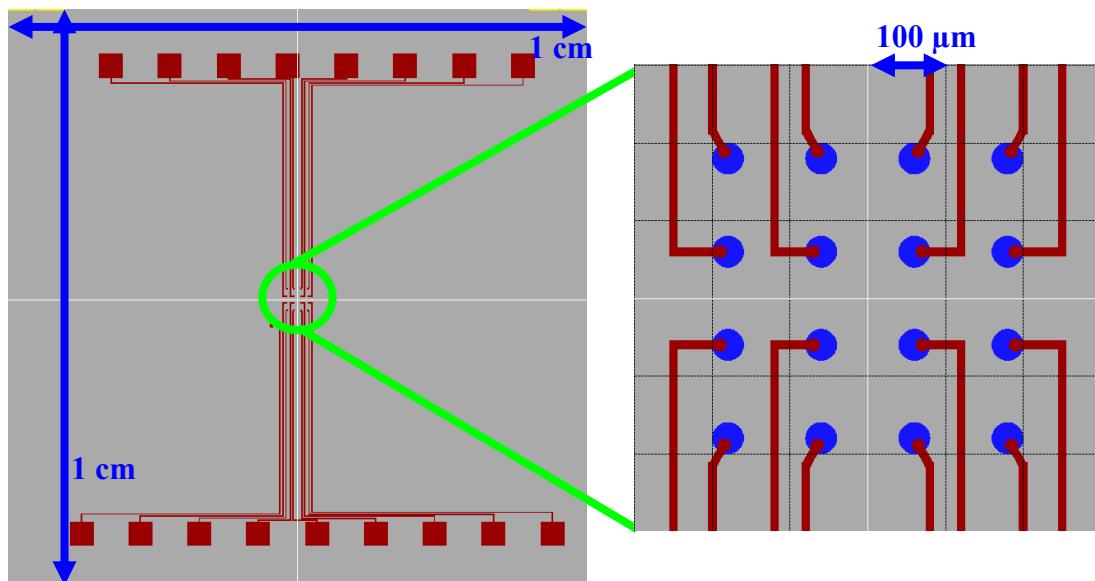

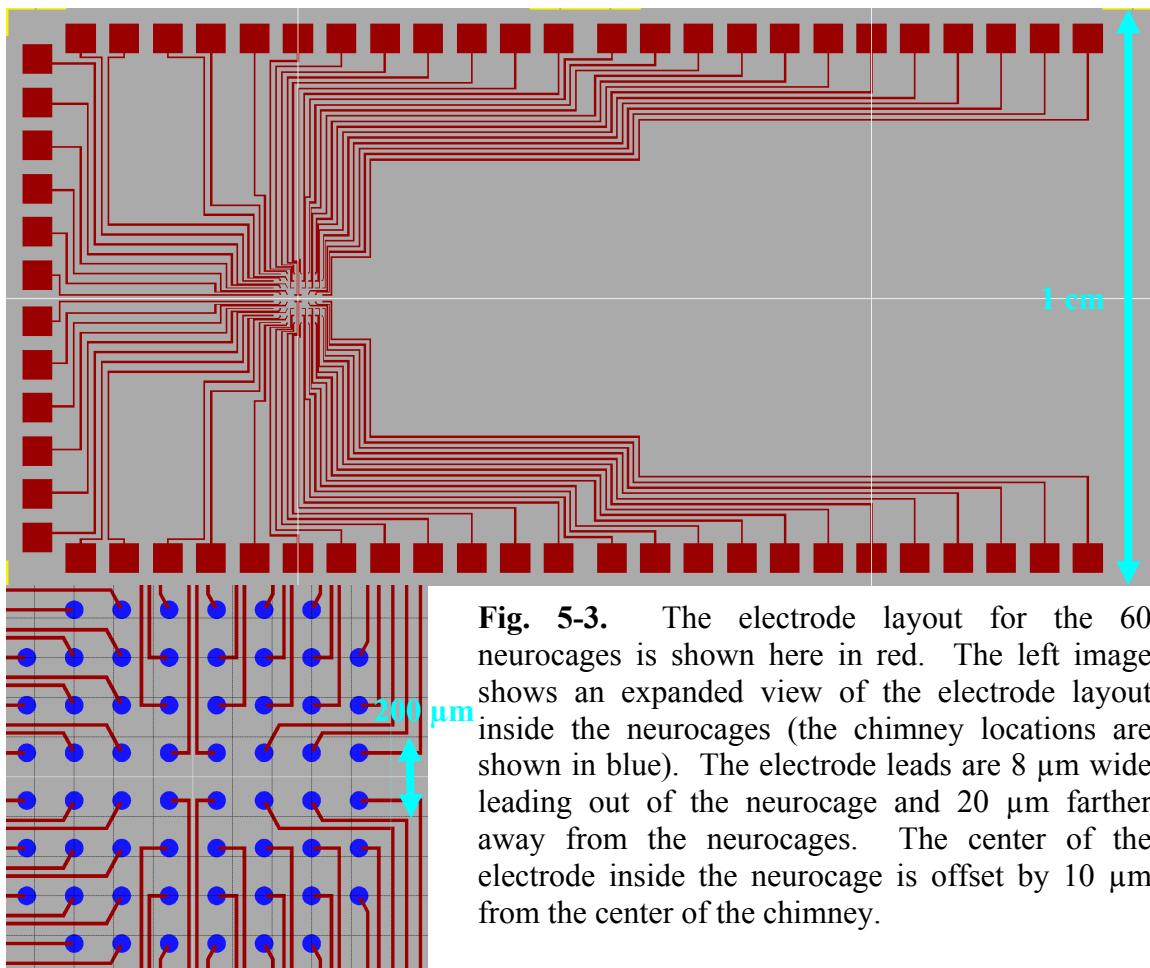

| <b>5-3.</b> Electrode layout for the array of 60 neurocages.....                                                                                                                 | <b>110</b> |

| <b>5-4.</b> Optical image of the anchors on glass and associated Newton rings.....                                                                                               | <b>112</b> |

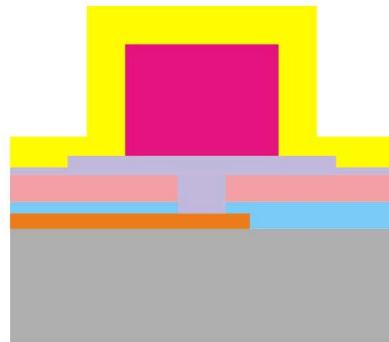

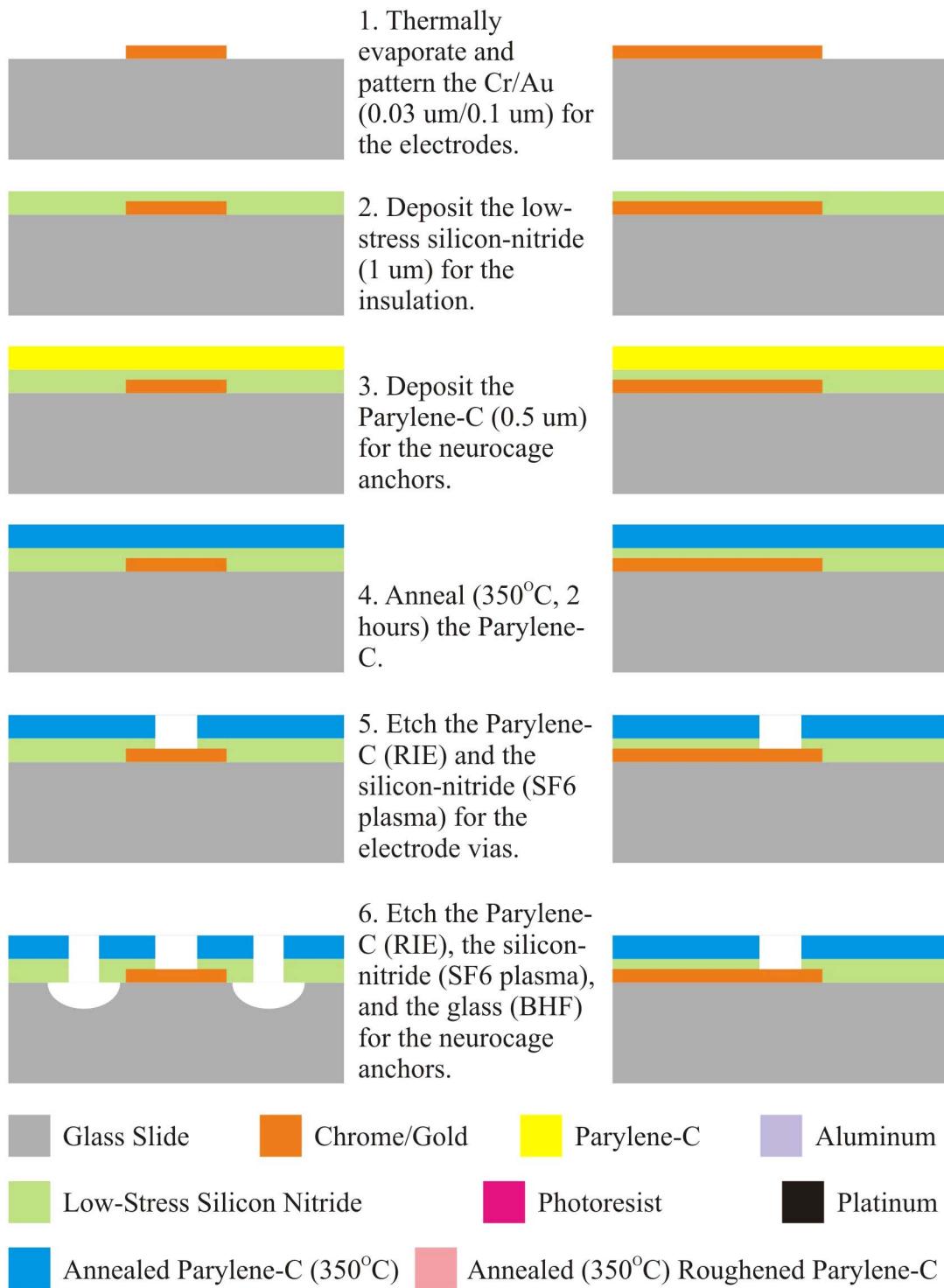

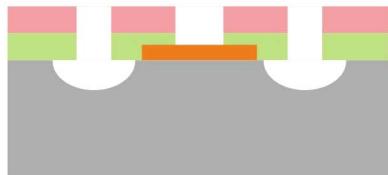

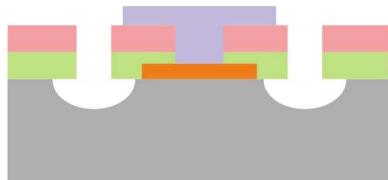

| <b>5-5.</b> Process flow for the neurocages on glass with Parylene-C insulation, sacrificial aluminum for the tunnels, and sacrificial soft-baked photoresist for the chimneys.. | <b>113</b> |

| <b>5-6.</b> Optical images of the chrome/gold electrodes for the neurocages.....                                                                                                 | <b>117</b> |

| <b>5-7.</b> Optical images of the neurocage anchors etched through the Parylene-C insulation and into the glass.....                                                             | <b>118</b> |

| <b>5-8.</b> Optical images of the aluminum tunnels on glass with Parylene-C insulation.....                                                                                      | <b>119</b> |

| <b>5-9.</b> Optical images of the aluminum etch stop on glass with Parylene-C insulation....                                                                                     | <b>120</b> |

| <b>5-10.</b> Optical images of the soft-baked photoresist chimneys on glass with Parylene-C insulation.....                                                                      | <b>121</b> |

| <b>5-11.</b> Optical images of the neurocages on glass with Parylene-C insulation, with both 25 $\mu\text{m}$ and 4 $\mu\text{m}$ long tunnels.....                              | <b>122</b> |

|                                                                                                                                                                                                      |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| <b>5-12.</b> SEMs of the neurocages on glass with Parylene-C insulation, with both 25 $\mu$ m and 4 $\mu$ m long tunnels.....                                                                        | <b>123</b> |

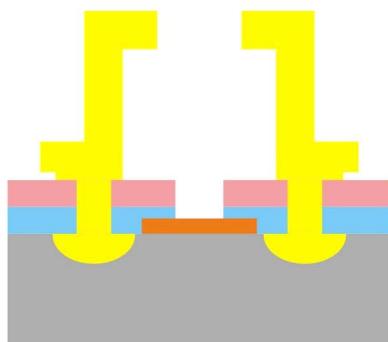

| <b>5-13.</b> Process flow for the neurocages on glass with low-stress silicon-nitride insulation, sacrificial aluminum for the tunnels, and sacrificial soft-baked photoresist for the chimneys..... | <b>126</b> |

| <b>5-14.</b> Optical images of the neurocage anchors on glass with low-stress silicon-nitride insulation.....                                                                                        | <b>130</b> |

| <b>5-15.</b> Optical images of the aluminum tunnels and soft-baked photoresist chimneys on glass with low-stress silicon-nitride insulation.....                                                     | <b>130</b> |

| <b>5-16.</b> Optical images of the neurocages on glass with low-stress silicon-nitride insulation, with both 25 $\mu$ m and 4 $\mu$ m long tunnels.....                                              | <b>131</b> |

| <b>5-17.</b> SEMs of the neurocages on glass with low-stress silicon-nitride insulation, with both 25 $\mu$ m and 4 $\mu$ m long tunnels.....                                                        | <b>132</b> |

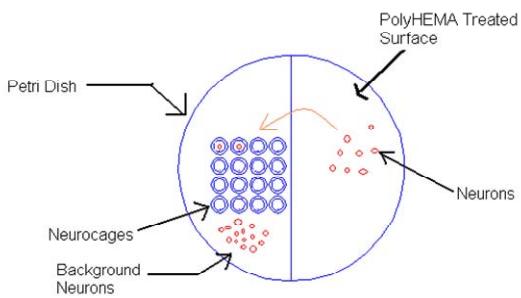

| <b>5-18.</b> Diagram of the culture dish with the neurochip attached.....                                                                                                                            | <b>134</b> |

| <b>5-19.</b> Optical images of neurons cultured inside neurocages on glass.....                                                                                                                      | <b>135</b> |

| <b>5-20.</b> Graph of the neuronal survival rate for neurons in neurocages on glass.....                                                                                                             | <b>135</b> |

# List of Tables

|                                                                                  |           |

|----------------------------------------------------------------------------------|-----------|

| <b>2-1.</b> Selected properties for Parylene-N, C, and D.....                    | <b>23</b> |

| <b>3-1.</b> Advantages and disadvantages of potential sacrificial materials..... | <b>30</b> |

| <b>4-1.</b> Dielectric constants for some insulating materials.....              | <b>54</b> |

# CHAPTER 1

## Neurons and Neural Networks

Neurons are at the heart of our biological and cognitive functions. The human brain consists of networks of more than 100 billion interconnected nerve cells. These neural networks control our perceptions, actions, emotions, and our ability to learn. Thus, neurons, and the neural networks they form, have been the subjects of intense study over the last several decades. Unfortunately, due to the location of these neural networks and their immense complexity, it is very difficult to study these networks *in vivo*. Therefore, the most common techniques for studying neural networks are *in vitro* techniques.

### 1.1 Neurons

A typical neuron can be divided into four separate regions: cell body, dendrites, axon, and presynaptic terminals. The cell body is the metabolic center for the neuron, processing proteins and nutrients. Dendrites and the axon are the processes of the neuron. The dendrites branch out from the cell body and receive incoming signals from other neurons. The axon extends out from the cell body and transmits electrical signals to other neurons. These electrical signals are called action potentials and are rapid, transient, all-or-none impulses. They have typical amplitudes of 100 mV with durations

of about 1 ms. Action potentials are the method by which the brain receives, analyzes, and conveys information. As all neurons conduct action potentials in the same manner, the information conveyed by the action potential is determined by the pathway to the brain and not the signal itself. Finally, the presynaptic terminals are at the ends of the axon and transmit the action potentials to the dendrites of the next neurons in the network.

There are two basic principles of neural organization, put forth by Ramón y Cajal [1]. The first is called the principle of dynamic polarization. This principle states that the electrical signals in the neurons flow in only one direction, from the dendrites to the cell body to the axon and finally to the presynaptic terminals. The second is the principle of connectional specificity. According to this principle, neurons do not indiscriminately form random neural networks; rather each neuron makes specific connections with only certain other neurons.

Ultimately, we want to study the dynamics of a functioning neural network by measuring the electrical activity of all of the individual neurons within the network. Our goal is to create a non-invasive technique that allows specific stimulation of selected neurons and records the responses of all the other neurons. Then we can map the connections within the neural network and study the plasticity, the changes over time in the connections between the neurons. There are two standard electrophysiological techniques for studying neurons within a neural network: whole-cell patch-clamp and multi-electrode arrays (MEAs).

## 1.2 Patch-Clamp Recording Technique

The patch-clamp technique developed in 1976 by Erwin Neher and Bert Sakmann involves puncturing the cell membrane with a glass micropipette filled with saline [1]. A metal electrode in contact with the saline in the micropipette allows the membrane current to be recorded. The properties of small to medium sized neural networks can be explored with this technique [2–3].

There are, however, several serious drawbacks to this technique. First, by puncturing the cell membrane, the neuron's responses can be unintentionally altered. The puncturing also leads to imminent neuron death, usually in a matter of hours. This limits the ability of the patch-clamp to obtain repeated recordings over long periods of time. In addition, the death of individual neurons in the neural network will alter the connections and function of the network. Finally, we would like to be able to record from all of the neurons within the neural network. However, the patch-clamp requires the use of large external micromanipulators to hold and manipulate the micropipettes, and given the relatively small area in which the neural network grows, it is virtually impossible to record from more than a few neurons at one time.

## 1.3 Multi-Electrode Arrays (MEAs)

Multi-electrode arrays (MEAs) are two-dimensional arrays of electrodes on glass or silicon substrates [4–9]. Neurons are cultured on top of the electrode array and neural networks are allowed to form. MEAs are non-invasive and non-lethal, unlike the patch-clamp technique, and are well-suited for long-term experiments. MEAs are ideal for

studying the spontaneous activity of the neural network, as well as recording action potentials when an external source supplies the stimulation pulse. MEAs are the standard method for neural network recording; however, they have two serious weaknesses when studying neural network function. First, the cell bodies and processes (axons and dendrites) are typically quite mobile during the first few weeks of culturing [10–12]. Thus, it is difficult to associate the recorded signals with specific neurons. Second, since the neurons are not confined to the electrodes, recording and stimulation can occur at unknown sites on an unknown, often changing, number of neurons.

As an alternative to the traditional MEA, a patterned MEA was developed [11–14]. The patterned MEA is also a two-dimensional array of electrodes; however, the surface has been patterned. Certain regions surrounding the electrodes are stamped with a neurophilic substance, such as poly-D-lysine which promotes attachment of the neurons to the substrate, while other regions are stamped with a non-adhesive substance, such as polyethylene glycol (PEG) to which neurons will not adhere. Therefore, the neuron growth, and the subsequent neural network formation, is confined to those areas which have been stamped with the neurophilic substance. Thus, even though the neurons are mobile, the area in which they can move has been limited. Unfortunately, despite the restricted neuron growth area, the patterned MEA has the same drawbacks as the traditional MEA. To counteract these difficulties, the neuro-well was developed.

## 1.4 Neuro-Well

The neuro-well is essentially a two-dimensional electrode array, except around each electrode a small “well” is placed into which a single neuron can be placed [10, 15–17]. Fig. 1-1 shows the basic neuro-well structure. The neuro-well is a bulk-micromachined silicon device. The wells are etched into the silicon and then covered with a silicon-nitride canopy. Individual neurons are placed into the wells, while the silicon-nitride canopy traps the neurons in close proximity to the electrodes. The canopy also contains openings to allow neurite outgrowth. Arrays of neuro-wells permitted the neurites from different neurons to form connections, thereby allowing the neurons to develop neural networks. With these neuro-wells, individual neurons in neural networks could be reliably stimulated and action potentials recorded for long-term studies.

One advantage of the neuro-wells is the one-to-one correspondence between neurons and electrodes. Hence, electrical recordings can be unambiguously associated with a single neuron. Also, by physically trapping the neurons, it is guaranteed that the neuron will always be in close proximity to the same electrode, ensuring it can always be

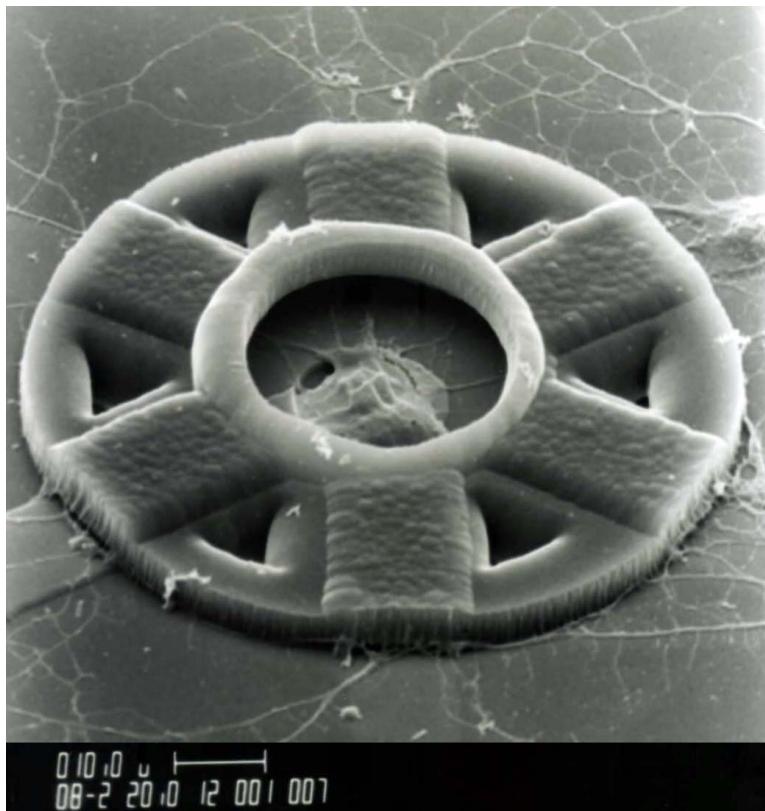

**Fig. 1-1.** The left image shows a scanning electron micrograph of a cross-section of the neuro-well. The electrode is at the bottom of the well and the silicon-nitride canopy covers it. The right image shows an illustration of a neuron inside the neuro-well, with the neurites extending out through the openings in the silicon-nitride canopy on top.

accessed. The recording and stimulation, like for the MEAs, is non-invasive and non-lethal, allowing individual neurons to be studied for long-term experiments.

Unfortunately, the neuro-wells had several significant drawbacks which limited their continued development. As the neuro-well was a bulk-micromachined device, the fabrication process was incredibly complex and the resulting devices had a very low yield. The complex fabrication process also made it difficult to create large arrays of neuro-wells to study large neural networks. Another serious flaw was that as the neurites grew out through the openings in the canopy on top of the wells, the neuron was pulled away from the bottom of the well, and hence from the electrode. In some cases, the neuron was pulled completely out of the neuro-well. Finally, the neuro-well was opaque, thus limiting the visibility of the cell bodies, making it difficult to ascertain details concerning the health of the neurons until after the neurites had grown out of the wells.

## 1.5 Neurocage

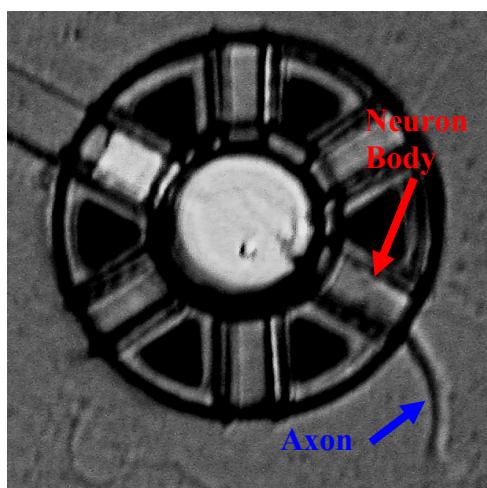

To counteract the difficulties encountered with the neuro-well, we developed the neurocage (Fig. 1-2), the focus of this thesis. Like the neuro-well, the neurocage traps individual neurons in close proximity to the electrodes, while at the same time allowing neurite outgrowth and neural network formation. The neurocage, unlike the neuro-well, is a surface micromachined device. Thus, the fabrication process is much less complex, resulting in a higher device yield. The use of surface micromachining techniques also makes it easy to fabricate large arrays of neurocages. Unlike the neuro-well, the neurites in the neurocage grow out through openings at the bottom of the cage. Hence, as the

**Fig. 1-2.** Illustration of a neuron inside the neurocage. The neurites grow out through openings in the bottom of the neurocage, pulling the neuron closer to the electrode. Thus, the neuron remains trapped in close proximity to the electrode.

neurites grow the cell body is actually pulled closer to the electrode, rather than further away. Finally, the use of Parylene, a biocompatible polymer described further in Section 2.2, ensures the neurocage is transparent. Thus, the neuron inside the neurocage can be easily visualized.

Initial neurocage designs achieved some neurite outgrowth, however, the long-term survival rate was very low (< 25%) [18–19]. The continued development of these neurocages presented here, achieves neurite outgrowth and neural network formation, with a long-term survival rate > 50%. In addition, successful action-potential stimulation and recording has been achieved from neural networks formed by neurons in these neurocages.

# CHAPTER 2

## MEMS Fabrication Technologies

A Micro-Electro-Mechanical System (MEMS) is a fabricated system that contains both electrical and mechanical components. The characteristic dimensions range from a 100 nm to millimeters. MEMS are also called micromachines or microsystems technology (MST). Inspired by the technologies used to create microelectronic devices, MEMS devices serve as bridges connecting the digital world of integrated circuits (IC) with the analog physical world.

MEMS technology is still largely based on techniques borrowed from the semiconductor industry. However, the materials and techniques used in MEMS fabrication are continually evolving to suit the current needs. Although still using the silicon-based devices common to semiconductor fabrication, alternative substrates, such as glass/quartz, ceramics, and polymers, are gaining popularity. This change is motivated by the desire to produce devices that are biocompatible, cheaper, and easier to fabricate.

In general, MEMS technology produces devices that are smaller, better, and cheaper. MEMS devices have significantly smaller footprints than their conventional counterparts. By exploiting phenomena that are better or more efficient with downsizing, MEMS devices are often faster, consume less power, and are more sensitive and selective.

## 2.1 Fabrication Technologies

Born out of the IC industry, many basic processing techniques for MEMS have been borrowed or adapted from those used to fabricate ICs. Some examples are photolithography, oxidation, diffusion, ion implantation, chemical vapor deposition (CVD), evaporation, sputtering, wet chemical etching, and dry plasma etching [20]. Many microfabrication techniques, such as bulk etching, Deep Reactive-Ion-Etching (DRIE), LIGA (German acronym for x-ray lithography, electroforming, and molding), wafer bonding, electroplating, and 3D-stereo lithography, have been specifically developed for MEMS over the years [21]. More recently, polymer-based MEMS have become popular, resulting in many new techniques suitable for polymers, such as soft lithography [22–24].

To make a complete MEMS device, several basic microfabrication processes are performed sequentially. These basic microfabrication processes can be classified as either bulk micromachining techniques [25] or surface micromachining techniques [26]. As shown in Fig. 2-1, bulk micromachining uses chemical or plasma selective etching of a substrate material, with the help of masking films, to form structures in the substrate. The etching process can be either isotropic, such as HNA (hydrofluoric acid + nitric acid + acetic acid) or  $\text{XeF}_2$ , or anisotropic, such as potassium hydroxide (KOH), tetra-methyl

**Fig. 2-1.** Examples of bulk micromachining and surface micromachining

ammonium hydroxide (TMAH), or DRIE. Surface micromachining, on the other hand, fabricates devices on top of the substrate, usually with the help of sacrificial materials, to form freestanding or even completely released thin-film microstructures, such as micro-channels and micro-cantilevers (Fig. 2-1). Common sacrificial materials used in surface micromachining are photoresist, polyimide, metals, phosphosilicate glass, and polysilicon.

The neurocage is, in general, a surface micromachined MEMS device, although it does utilize some of the bulk micromachining techniques. The basic techniques used in the neurocage fabrication are:

1. Photolithography

2. Oxidation

3. Etching (including both wet chemical and dry plasma etching)

4. Evaporation

5. Chemical Vapor Deposition or CVD (including Plasma-Enhanced CVD or PECVD)

These techniques are described in further detail in the subsequent sections.

### **2.1.1 Photolithography**

Photolithography is the basic tool to fabricate a MEMS device. By creating patterns with photoresist on the substrate, selective regions are then subjected to etching or deposition steps, thus transferring the pattern to the substrate [20–21]. Repeating this procedure of pattern definition followed by etching/deposition with different patterns allows the creation of complex MEMS devices.

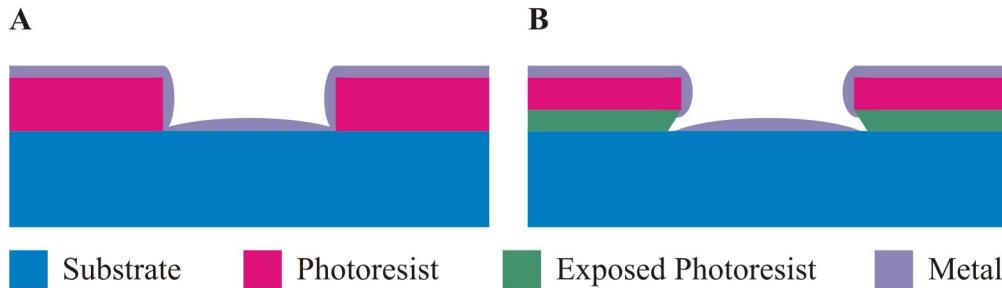

There are 3 basic steps to any lithographic process: photoresist application, exposure, and development (Fig. 2-2). The photoresist is a light-sensitive chemical that undergoes a chemical change when exposed to certain wavelengths of light (generally UV light). Conventional photoresists consist of 3 materials: solvent, matrix resin, and photoactive compound (PAC). The solvent keeps the photoresist in a liquid state until it is applied to the wafer and processed. Once the photoresist is spun onto the substrate, the substrate is then soft-baked, during which most of the solvent (approximately 80–90%) is baked out of the photoresist. After removal of the solvent, the matrix resin and the PAC remain. The matrix resin, in the absence of the solvent, provides the photoresist film with its adhesion and etch resistance properties. In other words, the matrix resin ensures the photoresist adheres to the substrate during the subsequent exposure and development steps. In addition, the matrix resin determines the thickness of the photoresist and resists the chemical or plasma etching that follows photoresist development. The last component of conventional photoresists is the PAC. The PAC undergoes a chemical

**Fig. 2-2.** Illustration of the photolithography process for both positive and negative photoresists

reaction in response to exposure to UV light, which then determines the etch rate of the photoresist in developer. In positive photoresists, the PAC, once exposed to UV light, acts as a catalyst, increasing the rate at which the resist will dissolve when placed in the developing solution. In contrast, the PAC in negative photoresists, after exposure to UV light becomes cross-linked and acts as an inhibitor, decreasing the rate at which the resist dissolves when placed in the developing solution.

Once the photoresist is spun on and soft-baked, it is then exposed to UV light through a mask. The mask contains transparent and opaque features that define the pattern to be transferred to the photoresist. The exposure to the UV light activates the PAC, rendering the areas of the photoresist either soluble or insoluble to developing. After exposure, the developer dissolves either the exposed regions of the photoresist (in the case of positive photoresist) or the unexposed regions of the photoresist (in the case of negative photoresist). In both cases, once developing is complete, the features in the mask will have been faithfully replicated in the photoresist. At this point, the exposed substrate can be subjected to a variety of etching or deposition processes. The presence of the photoresist protects the substrate in those regions from the etching or deposition processes. Thus, the features in the masks can be successfully replicated on the substrate.

### 2.1.2 Oxidation

Silicon dioxide ( $\text{SiO}_2$  or oxide) is used in a variety of MEMS applications, including as an insulator for electrodes, mask material for etching processes, and sacrificial material for surface micromachining [20]. There are two main processes for

depositing oxide onto a substrate: thermal oxidation (requires a silicon substrate) and sputtering.

### 2.1.2.1 Thermal Oxidation

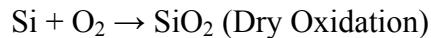

Thermal oxidation involves heating a silicon substrate in an O<sub>2</sub>-containing atmosphere [20–21]. Although silicon oxidizes readily in ambient air, even at room temperature, creating native oxide layers approximately 20 Å thick, the elevated temperatures allow thicker layers of oxide to be grown. The high temperature, generally between 600°C and 1250°C, aids in the diffusion of the oxidizing material through the oxide present on the surface to the silicon interface, where it then converts the silicon to oxide. The oxidizing material is either water vapor (wet oxidation) or O<sub>2</sub> gas (dry oxidation). The governing reactions that convert the silicon to oxide are:

Thermal oxidation is good for growing thin layers of oxide (< 1 µm), which is more than sufficient for most insulating and masking applications. The drawback of thermal oxidation is that the silicon must be free of all metal or polymers, as these materials cannot generally withstand the high temperature and will interfere with the oxidation reaction. This limits the use of thermal oxide as a sacrificial material.

### 2.1.2.2 Sputtering

Sputtering is a general technique used for the deposition of a wide variety of materials, including oxide, silicon, metals, silicon-nitride, and polysilicon [20–21].

During sputtering, the target (a disc of the material to be deposited) is held at a high negative potential. Positive ions of an inert gas, such as argon or xenon, bombard the target which causes neutral atoms of the target material to be sputtered off. The bombardment, and subsequent sputtering, transfers the momentum of the positive ions to the neutral atoms allowing the neutral atoms to travel to and condense on the substrate.

The use of sputtering to deposit oxide layers does not limit the choice of substrate and sputtered oxide can be deposited on silicon, metal, and polymers. Similar thicknesses are achievable with both sputtered and thermal oxide, although sputtered oxide does not require high temperatures for deposition. Thus, sputtered oxide is ideal for use as a sacrificial material. However, as it often contains impurities, it is less ideal as an insulating material.

### 2.1.3 Etching

The two main types of etching are wet etching and dry (including plasma) etching [20–21]. Although wet etching is often faster and can provide better selectivity than dry etching, it also requires the use of potentially dangerous acids and solvents. As such, dry etching techniques, requiring only small amounts of chemicals are generally preferred. Some of the other advantages obtained by dry etching are both isotropic and anisotropic etch profiles, directional etching (independent of the crystal orientation of the underlying silicon), high-resolution patterns, and better process control.

### 2.1.3.1 Wet Etchants

The basic wet etching process involves three fundamental steps. First, the reactants must be transported to the surface. Second, a surface reaction occurs between the reactants and the material to be etched. Finally, the products of the surface reaction must be transported away from the surface. In general, wet etchants contain three key ingredients: an oxidizer, an acid or base to dissolve the oxidized surface, and a diluent in which the reactants and products are transported. Wet etchants can be used to etch silicon, oxide, silicon-nitride, and metals.

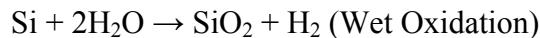

Wet etchants can be further classified by the etching profile they produce (Fig. 2–3). Isotropic etchants have the same etch rate in all directions. In other words, the lateral etch rate is the same as the vertical etch rate, and these are independent of the mask or substrate orientation. These etchants will undercut the mask layer if etching continues long enough. For anisotropic etchants, the etch rate depends on the crystal orientation of

**Fig. 2-3.** These illustrate the differences between isotropic and anisotropic wet etching. The left image shows a time series for isotropic wet etching. As the vertical etching continues, the masking material is undercut as the etching also continues laterally. The right image shows two possible anisotropic etching profiles. As can be seen, the masking material is not undercut.

the material to be etched. Thus, the lateral etch rate can be significantly larger or smaller depending upon the orientation of the mask to the crystalline axes of the substrate.

### 2.1.3.2 Dry Etchants

There are two main types of dry etching: non-plasma based and plasma based. Non-plasma-based dry etchants are isotropic and generally limited to etching silicon. These etchants typically are fluorine-containing gases, such as xenon difluoride or bromine trifluoride, that readily etch silicon. The etch rate is easily controlled by the temperature and pressure of the reactants.

Plasma-based dry etching (plasma etching) employs the use of plasma to etch the substrate. Plasma is a partially ionized gas consisting of equal numbers of positively (ions) and negatively (electrons) charged species, as well as a large number of neutral (un-ionized molecules). Ion-electron pairs are constantly created by ionization and destroyed by recombination. Plasma is generated by filling a chamber with the required gases and applying DC or RF energy to a pair of electrodes. The applied energy accelerates the electrons, thereby increasing their kinetic energy. The electrons collide with the neutral gas molecules forming more ions and electrons. Plasma is created when steady state is reached and the ionization rate of the molecules equals the recombination rate. Like wet etchants, plasma etching can be used to etch silicon, oxide, silicon-nitride, and metals. In addition, plasma etching can be used to etch organic films, including photoresist and polymers.

There are four types of plasma etching: physical etching, chemical etching, Reactive-Ion Etching (RIE), and Deep Reactive-Ion Etching (DRIE). Physical etching

(often called sputter etching) is based on the physical bombardment of the substrate with ions. The plasma is used to energize a chemically inert molecule. When this molecule strikes the surface, the substrate atoms are dislodged. Physical etching is highly anisotropic, although it has very low-selectivity, often etching the masking material at the same rate as the underlying substrate. In chemical etching, the plasma is used instead to produce chemically reactive species from the gas. These chemically reactive species diffuse and adsorb to the surface, react with the surface molecules to be etched, and the resulting products are desorbed and diffuse away. This isotropic etching process is similar to the wet etching process. The RIE process is actually a combination of physical and chemical etching. The chemical etching is assisted by the ionic bombardment (physical etching), as the bombardment creates more areas for the chemical reactions to occur. The RIE process, because of the ionic bombardment, is more anisotropic and faster than the chemical etching process, however, it also has much lower selectivity. The DRIE process uses inductively coupled plasma (ICP) technology or microwave electron cyclotron resonance (ECR) to create the plasma [27–29]. This creates a high-density, low-pressure, low-energy plasma, leading to increased etch rates, high selectivity, increased ion directionality (resulting in less side-wall etching), and less damage (caused by ion bombardment). Thus, the DRIE process is highly anisotropic, with very large aspect ratios possible.

#### 2.1.4 Evaporation

A variety of different kinds of films can be deposited by evaporation [20–21]. Both evaporation and sputtering (described in Section 2.1.2.2) are examples of physical

vapor deposition (PVD) in which the material to be deposited is first vaporized from a source and then condensed onto the substrate. Evaporation is one of the oldest techniques for depositing thin films (generally metals). Thermal evaporation is based on the boiling off, or sublimating, of metal onto a substrate. It is generally performed under vacuum to eliminate any potential contaminants (including oxygen which can oxidize the deposition metal) and to increase the mean free path of the molecules boiled off, ensuring the majority of them reach the substrate. The two primary means for heating the deposition material are resistive and electron beam (often called e-beam evaporation). In resistive heating, the metal is contained in a highly resistive container (e.g., a tungsten boat) and a high current is passed through the container heating it and causing the metal to evaporate. In electron beam heating, an electron beam is magnetically focused onto the target metal causing it to locally melt and evaporate.

As mentioned in Section 2.1.2.2, it is possible to deposit metal films using sputtering. Some advantages of using evaporated metal are higher deposition rates, less substrate heating, and fewer impurities, due both to the higher vacuum and the fact that in evaporation a new charge of metal is used for each deposition, as opposed to sputtering where the target is re-used for multiple depositions.

### **2.1.5 Chemical Vapor Deposition (CVD)**

The basic mechanism of chemical vapor deposition (CVD) is that starting material is vaporized and then chemically reacts with the molecules on the surface to create the desired deposited material [20–21]. CVD starts by moving the reactant gases (often diluted with an inert carrier gas) into the main reaction chamber. As the gases

flow through the chamber, the reactant gas transports to the surface. The reactants, now called adatoms, are adsorbed onto the substrate surface. The adatoms migrate to the growth sites where the film-forming reactions take place creating the solid film and gaseous by-products. Once the gaseous by-products are desorbed from the surface, the gas flow through the reaction chamber removes the gaseous by-products. The energy to drive these chemical reactions can be supplied by several different methods: thermal energy, photonic energy, or electrons. There are a variety of different types of CVD classified by the pressure at which the deposition takes place: Atmospheric-Pressure (APCVD), Low-Pressure (LPCVD), and Plasma-Enhanced (PECVD).

In PECVD, plasma is responsible for creating the radicals that eventually form the deposited films. The ion bombardment of the substrate provides the energy required to form the film. APCVD and LPCVD both rely on thermal energy for creating the radicals and forming the film. The main advantages of PECVD are the lower substrate temperature required, in the range of 300°C to 400°C, and the good step coverage. PECVD is ideal for low-temperature insulators, such as silicon-nitride. LPCVD also achieves good step coverage, although the deposition rate is less than that for PECVD. It is ideal for high-temperature oxides, silicon-nitride, and polysilicon. Unfortunately, LPCVD requires substrate temperatures in the range of 550°C to 600°C. APCVD, like PECVD, does not require high temperatures and has a high deposition rate. However, APCVD has poor step coverage.

## 2.2 Parylene

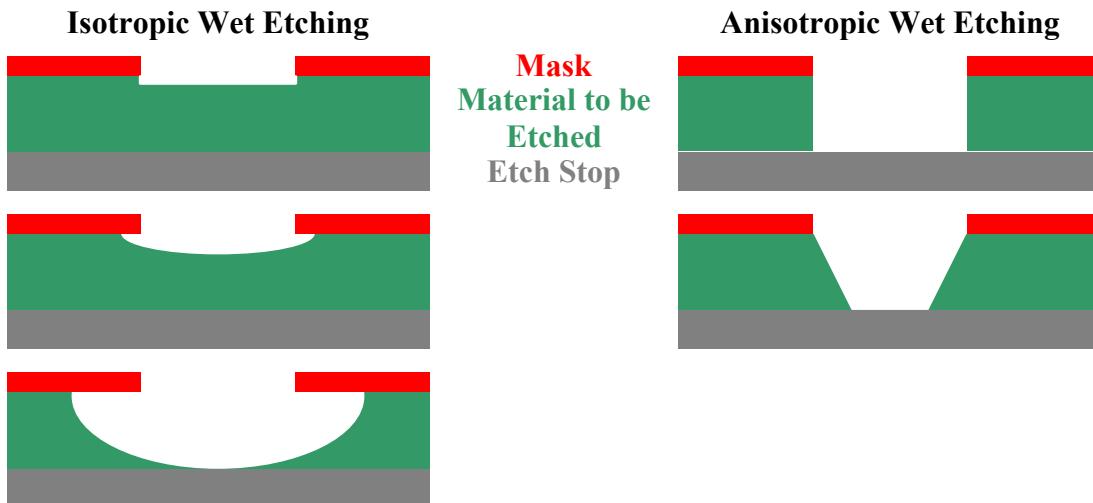

Parylene (poly-para-xylylene) is the generic name for a family of vapor phase deposited thermoplastic polymers [30]. Fig. 2-4 shows the chemical structures for the three most commonly used types of Parylene: Parylene-N, Parylene-C, and Parylene-D.

**Fig. 2-4.** Chemical structures for the three most common types of Parylene

### 2.2.1 Parylene Deposition

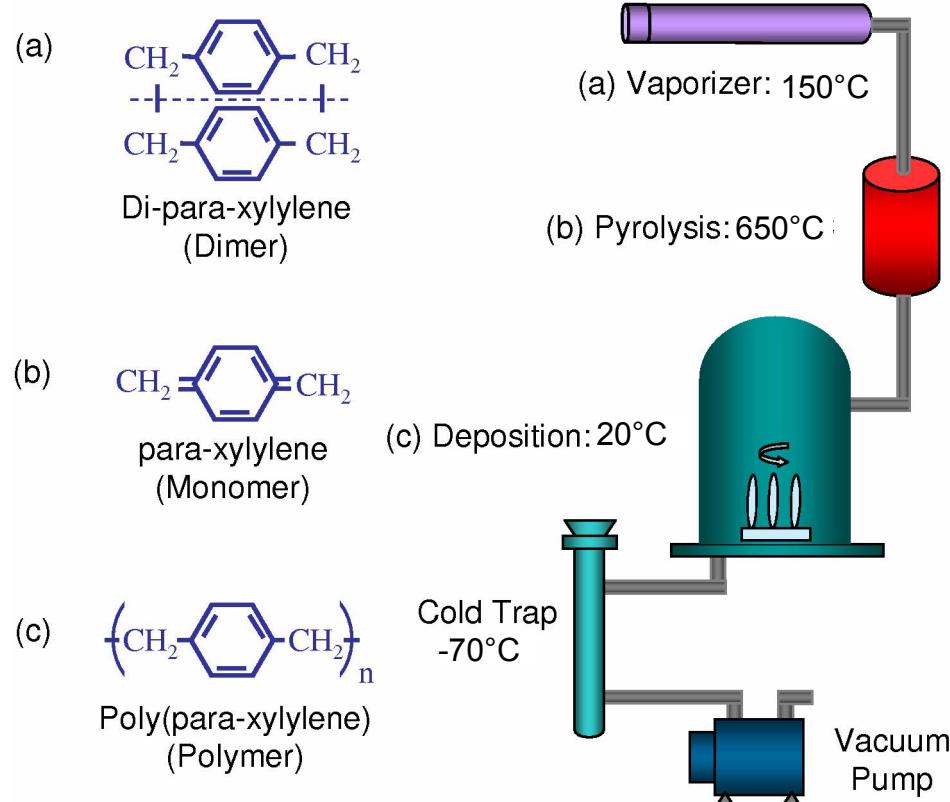

Parylene is deposited at room temperature using CVD [30]. The deposition process and corresponding chemical changes are shown in Fig. 2-5. This figure details the deposition process for Parylene-N; however, the process is identical for all three common types of Parylene, except for some slight differences in pyrolysis temperature and deposition pressure.

To start, Parylene dimer (di-para-xylylene), a stable, granular compound, is placed in the vaporizer and the substrate to be coated in the deposition chamber. The whole system is pumped down to medium vacuum ( $\sim 10$  mTorr). The dimer is heated in the vaporizer until it sublimates at about  $160^\circ\text{C}$ . The dimer vapor enters the pyrolysis furnace, which is heated to  $690^\circ\text{C}$ , where it is cleaved into monomers (para-xylylene). In the room temperature deposition chamber, the monomers reunite on all exposed surfaces as the polymer poly-para-xylylene. The deposition takes place at the molecular level as the monomers are extremely active with a mean free path on the order of 1 mm (under

**Fig. 2-5.** Schematic of the Parylene deposition system and the associated chemicals. This process shows the deposition parameters for Parylene-N. The same procedure is used for the deposition of both Parylene-C and D, with slight changes in deposition pressure and pyrolysis temperature.

the deposition pressure of  $\sim 100$  mTorr). This results in superior penetration power and a high degree of conformability to the surfaces being coated. The temperature of the coated substrate inside the deposition chamber never rises more than a few degrees above room temperature.

The deposited Parylene film is highly conformal and truly pinhole free. Typical coating thicknesses range from one to tens of microns, although they can be as thin as hundreds of angstroms. The coating thickness is controlled by the amount of dimer used. The average deposition rate for Parylene-C is about  $5 \mu\text{m}$  per hour. The deposition rate is

directly proportional to the square of the monomer concentration and inversely proportional to the absolute temperature [30].

### 2.2.2 Parylene Properties

Parylene is an excellent barrier to gas and moisture. In addition, Parylene is extremely inert to most chemicals and solvents. Based on the manufacturer's study [30], solvents can cause minor swelling in Parylene, causing a 3% maximum increase in film thickness. This swelling is completely reversible, however, after the solvents are removed by vacuum drying. Inorganic reagents, except for oxidizing agents at elevated temperatures, have little effect on Parylene. Parylene is also biocompatible (USP Class VI), which means it is safe for long-term human implants. These properties also make Parylene well-suited for cell culture experiments.

Parylene exhibits impressive mechanical strength and flexibility in thin film coatings. Thus, it can be used to make both rigid structures and flexible actuators.

Parylene is also an excellent electrical insulator [31–36], as well as a good thermal insulator.

Optically, Parylene is transparent in the visible light range. It only absorbs light with wavelengths under 280 nm.

Due to their slightly different chemical structures, the three types of Parylene also differ in properties. Parylene-N has the best penetration characteristics; however, it also has the slowest deposition rate. Parylene-D can withstand higher temperatures than Parylene-C. Parylene-C, though, has a useful combination of electrical and physical properties, plus a very low permeability to moisture and corrosive gases. In addition, the

deposition rate of Parylene-C is faster than the other two types. Therefore, Parylene-C is the choice for most biological and electrical applications, including the neurocage.

Detailed electrical, mechanical, thermal, barrier, optical, and other properties can be found on a Parylene vendor's website [30]. A list of selected properties for Parylene-N, C, and D are shown in Table 2-1.

|                                                                               | Parylene-N | Parylene-C | Parylene-D |

|-------------------------------------------------------------------------------|------------|------------|------------|

| <b>Dielectric Constant (1kHz)</b>                                             | 2.65       | 3.10       | 2.82       |

| <b>Volume Resistivity (x10<sup>16</sup> Ω-cm)</b>                             | 14         | 8.8        | 12         |

| <b>Young's Modulus (GPa)</b>                                                  | 2.42       | 2.76       | 2.62       |

| <b>Density (g/cm<sup>3</sup>)</b>                                             | 1.1        | 1.3        | 1.4        |

| <b>Melting Temperature (°C)</b>                                               | 420        | 290        | 380        |

| <b>Glass Transition Temperature (°C)</b>                                      | N/A        | 80-100     | N/A        |

| <b>Thermal Conductivity at 25°C (mW/(cm-K))</b>                               | 1.26       | 0.84       | N/A        |

| <b>Moisture Vapor Transmission at 90%RH, 37°C (g-mil/100in<sup>2</sup>-d)</b> | 1.5        | 0.21       | 0.25       |

| <b>Water Absorption (% after 24 hours)</b>                                    | <0.1       | <0.1       | <0.1       |

**Table 2-1.** Selected properties for Parylene-N, C, and D

# CHAPTER 3

## Neurocages on Silicon without Electrodes

Neurocages allow individual neurons within a larger neural network to be stimulated and action potentials to be recorded. The “cage” structure counteracts the problems encountered when using multi-electrode arrays in which the lack of neuron-to-electrode specificity and the inherent neuron mobility make it difficult to stimulate and record from single neurons during long-term studies [10–12]. The surface micromachining techniques used in the fabrication of the neurocages eliminate the fabrication difficulties common to other bulk micromachined “cages,” such as the neuro-well [10, 15–17].

Three essential elements must be determined to create a functional neurocage, capable of stimulating and recording. First, a proper geometry must be found, one capable of both effectively trapping neurons and allowing neurite outgrowth to form neural networks. Second, suitable materials for fabricating the neurocage must be selected. Finally, a fabrication process to integrate the materials to create the desired geometry must be developed.

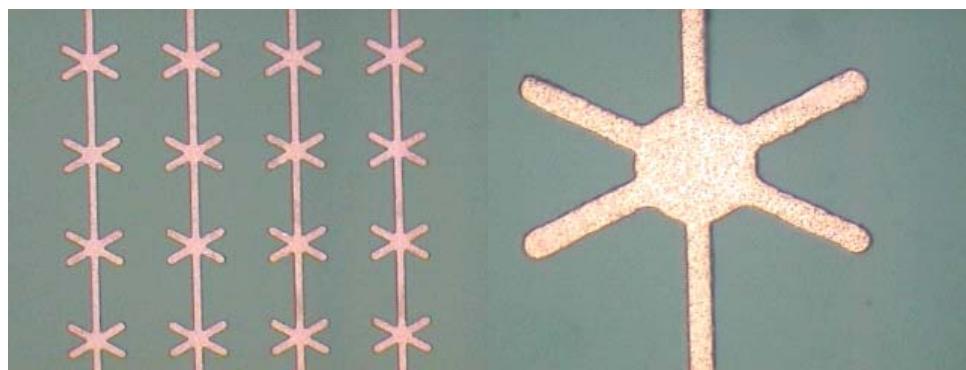

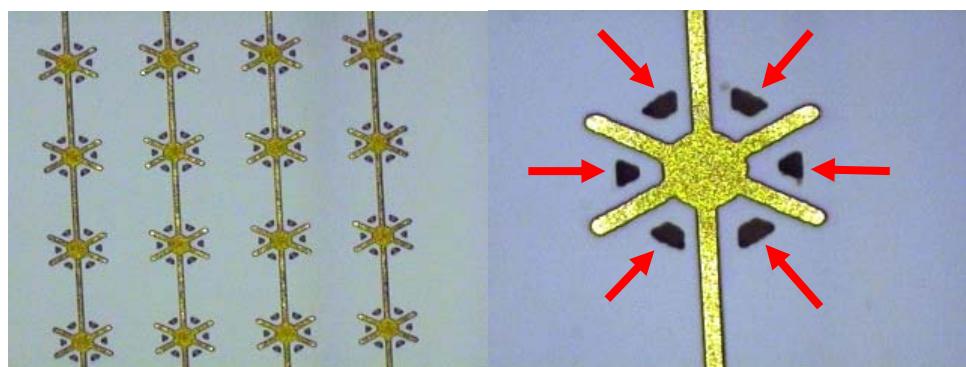

### 3.1 Design Components

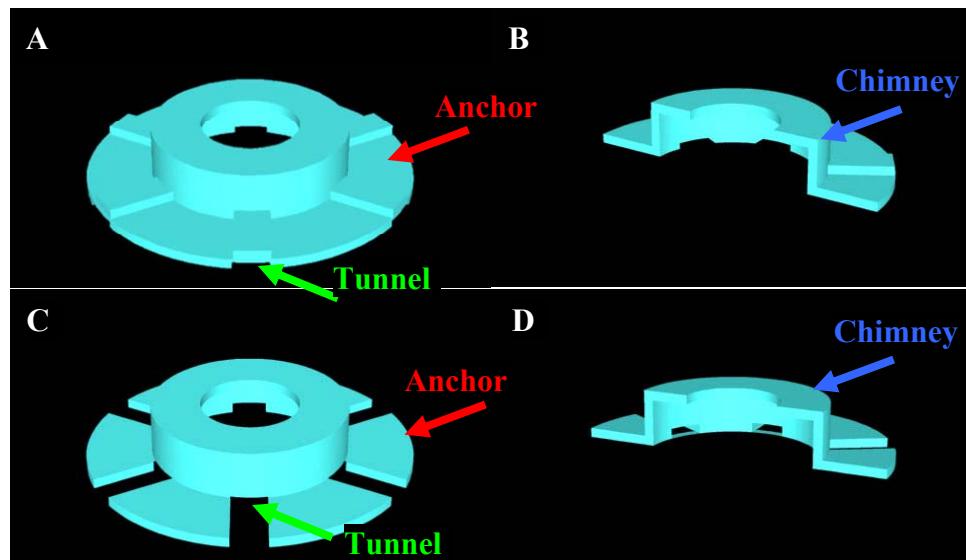

The three basic components of the neurocage are the anchors, the tunnels, and the chimney (Fig. 3-1). The anchors ensure the neurocage remains firmly attached to the substrate. The tunnels, while small enough to prevent the neurons from escaping the neurocage, are large enough to permit neurites to extend out of the neurocage and form synaptic connections with neighboring neurons. The chimney, including the loading hole through which the neuron is placed into the neurocage, is the central area in which the neuron lives and grows.

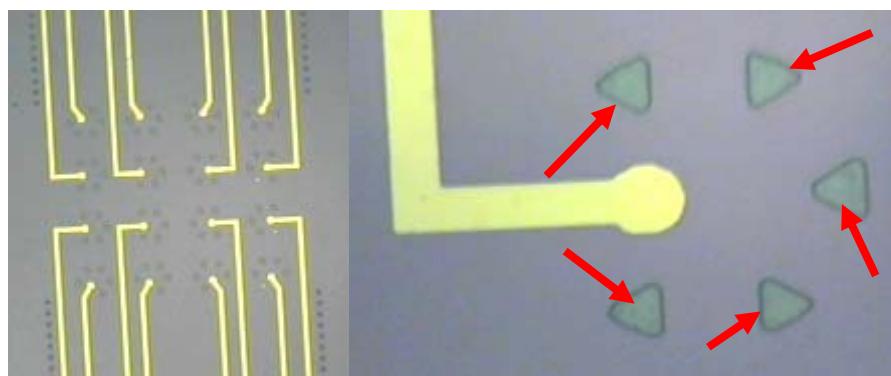

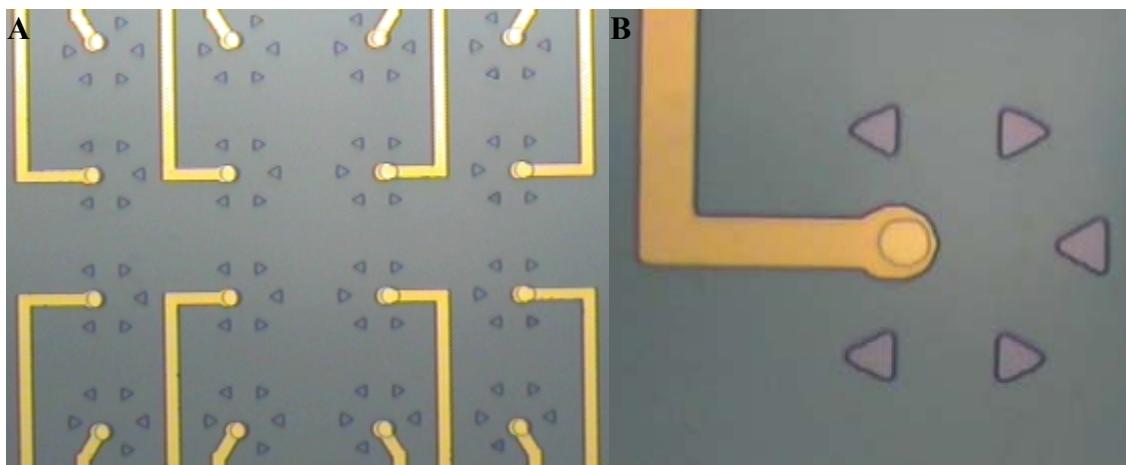

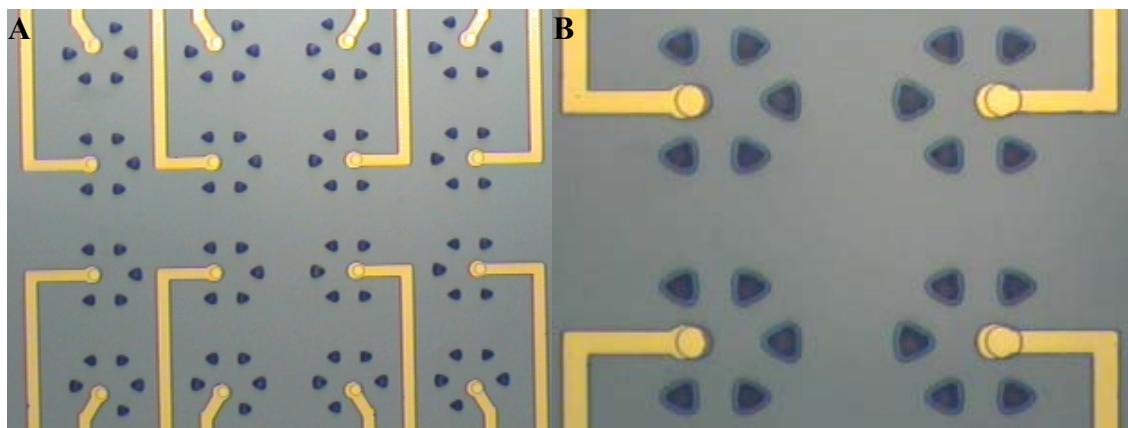

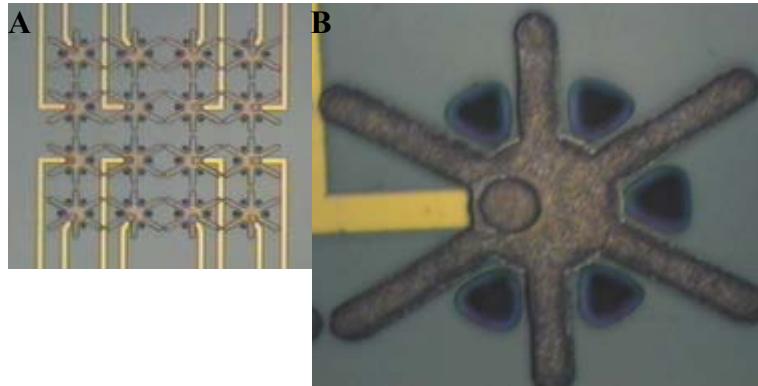

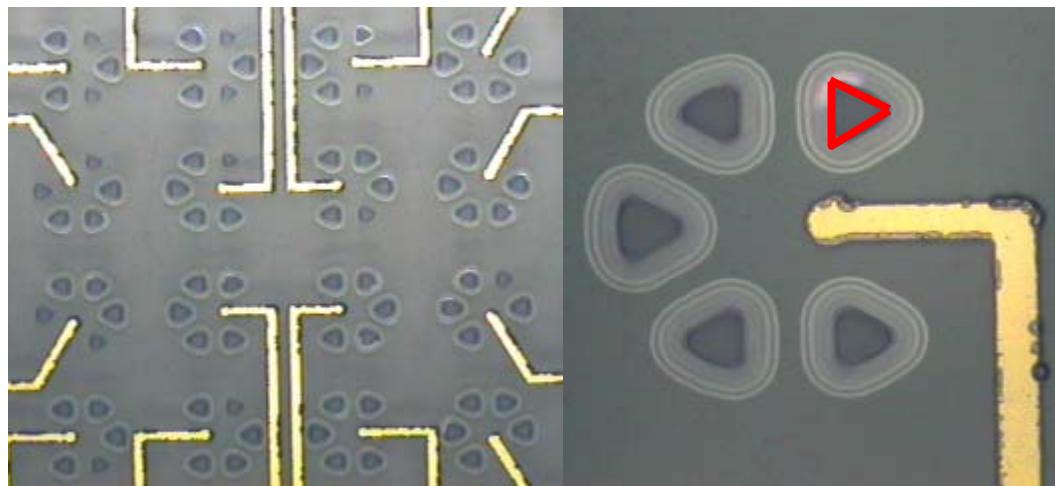

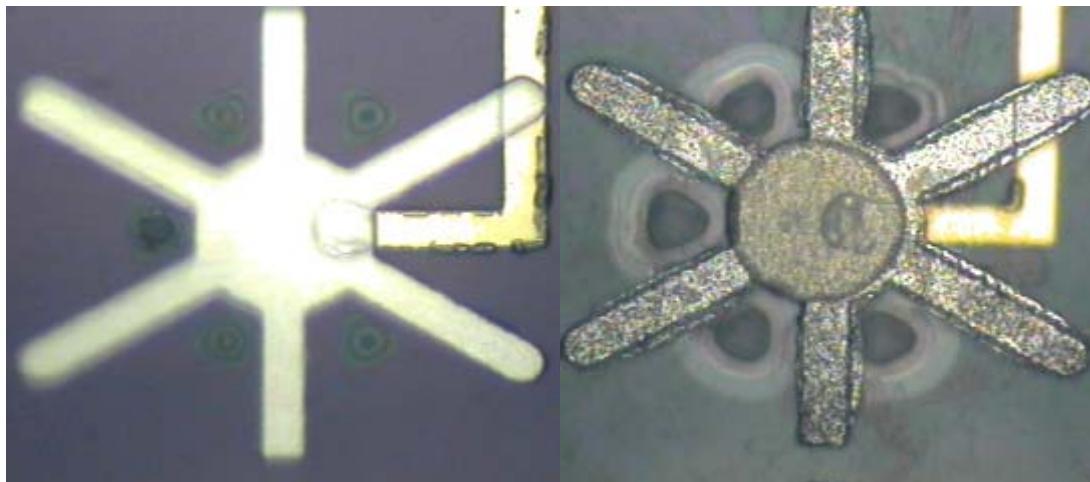

**Fig. 3-1.** Two different neurocage designs: long tunnels (A and B) and short tunnels (C and D). The arrows denote the anchors (red), tunnels (green), and chimneys (blue). (Not drawn to scale)

#### 3.1.1 Anchors

The Parylene-C used to form the neurocage does not adhere well to the silicon substrate. Chemical methods, such as the A-174 Parylene Adhesion Promoter (gamma-Methacryloxypropyltrimethoxy Silane, Specialty Coating Systems, Indianapolis, IN),

generally used to improve the adhesion between Parylene-C and the silicon are not effective for the neurocage due to the extremely small area that is in direct contact with the silicon. Hence, the neurocages require a structural method to anchor the Parylene-C to the silicon.

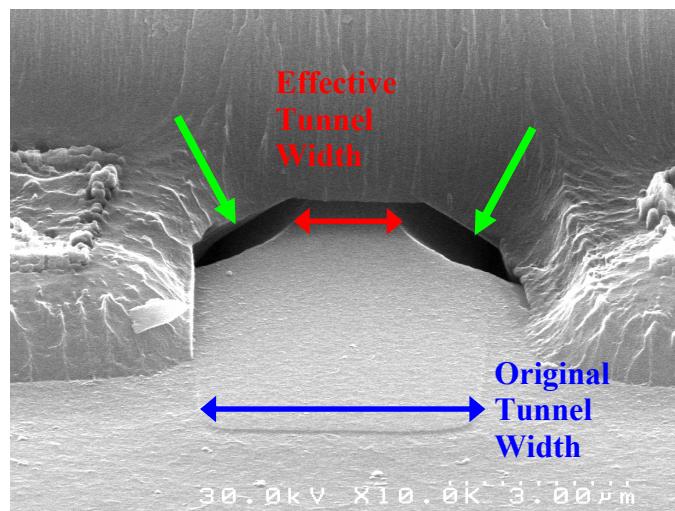

One structural method for creating anchors is to roughen the silicon, using gas-phase etchants, like xenon difluoride ( $XeF_2$ ) or bromine trifluoride ( $BrF_3$ ), or wet etchants, such as HNA (a mixture of hydrofluoric, nitric, and acetic acids). This increases the surface area of the silicon to which the Parylene-C will be in contact, without increasing the total area of the neurocage. Other chemical methods can also be used in conjunction with the roughened silicon to further improve the adhesion. Unfortunately, while the roughened silicon improves adhesion, the etchants are isotropic and can produce severe undercut of the neighboring tunnels (Fig. 3-2). This decreases the effective tunnel width through which the neurites can grow. If the tunnels are too narrow, the neurons will not extend through the tunnels and, thus, will not form synaptic

**Fig. 3-2.** Scanning electron micrograph of a tunnel and anchors etched with  $XeF_2$ . The green arrows denote the anchor undercut extending into the tunnels, effectively narrowing the tunnel.

connections with nearby neurons.

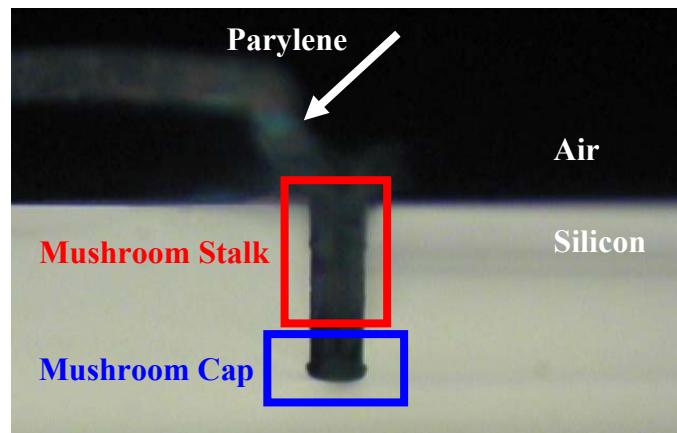

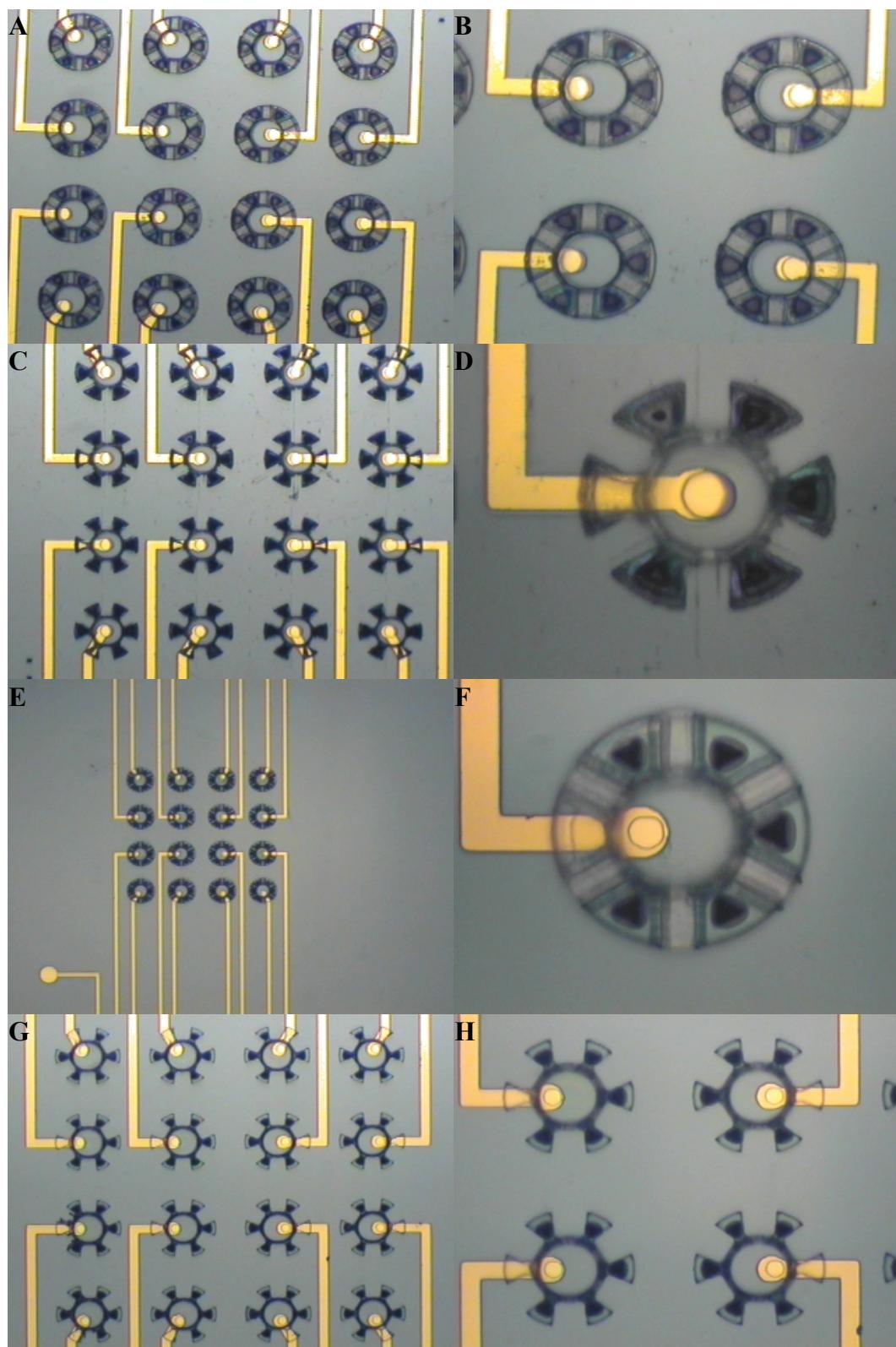

An alternative method uses a combination of isotropic and anisotropic etchants to create a locking structure, with virtually no undercut. This process uses Deep-Reactive-Ion Etching (DRIE) to create an inverted mushroom structure that, when filled with Parylene-C, securely anchors the Parylene-C to the silicon (Fig. 3-3) [37]. First, a standard Bosch process [38] is used to create the vertical “mushroom stalk.” The Bosch process uses alternating sulfur hexafluoride ( $SF_6$ ) and fluorocarbon ( $C_4F_8$ ) plasmas. A short exposure to  $SF_6$  plasma will etch the silicon isotropically. The  $C_4F_8$  plasma then creates a Teflon-like passivation layer on the bottom and sidewalls of the hole. This passivation protects the sidewalls from further etching during the subsequent exposures to  $SF_6$  plasma. The bottom is not protected from etching by the passivation layer since the  $SF_6$  ions are directional in the DRIE and travel vertically down the hole. Thus, the passivation layer at the bottom is quickly etched off by the  $SF_6$  ions, exposing the silicon for etching by the  $SF_6$  plasma. Repeating this alternating etching and passivation process

**Fig. 3-3.** Scanning electron micrograph of an anchor etched into silicon and filled in with Parylene-C. The red outlines the anisotropically etched mushroom stalk and the blue outlines the isotropically etched mushroom cap.

yields a highly anisotropic structure that forms the mushroom stalk. Next, a longer SF<sub>6</sub> plasma etch creates the “mushroom cap.” The sidewalls are still protected from etching by this SF<sub>6</sub> plasma etch from the previous C<sub>4</sub>F<sub>8</sub> passivation step (the last step in the Bosch process creating the mushroom stalk), so only the bottom is etched isotropically by the SF<sub>6</sub> plasma. Since the Parylene-C deposition is conformal, this inverted mushroom structure will be completely filled by the Parylene-C forming the neurocages. This method, unlike the first method, does not rely on the adhesion of the Parylene-C to the silicon, but rather mechanically locks the Parylene-C to the silicon creating a more robust structure capable of withstanding a variety of chemical and mechanical treatments and increasing the reusability of the neurocages. In addition, the mostly anisotropic etching process virtually eliminates any undercut, ensuring that the tunnels remain the desired width.

Each neurocage has six anchors. The anchors are approximately trapezoidal, with an area of 60  $\mu\text{m}^2$  or 90  $\mu\text{m}^2$ , for 10  $\mu\text{m}$  or 5  $\mu\text{m}$  wide tunnels, respectively. The anchors and the tunnels are interleaved with one another and separated by 4  $\mu\text{m}$ . The separation allows for slight misalignment of the various layers during fabrication. The anchors are 50–60  $\mu\text{m}$  deep, although the depth of the anchors is not critical, provided the inverted mushroom structure is present.

### 3.1.2 Tunnels and Chimneys

The neurocages each have six tunnels and one chimney. The size of the neurons used for the experiments dictates the dimensions of the tunnels and chimney. These experiments used embryonic rat neurons, which are approximately 10–15  $\mu\text{m}$  in diameter

when loaded into the neurocages and grow to be approximately 25  $\mu\text{m}$  in diameter. The neurons flatten themselves against the bottom silicon surface as they extend their neurites; hence when full grown, the neurons are more like a thin disc rather than a sphere. Based on this information, the chimney was designed to be 30  $\mu\text{m}$  in diameter and between 4  $\mu\text{m}$  and 15  $\mu\text{m}$  tall. The neurites are cylindrical, approximately 1  $\mu\text{m}$  in diameter, and can grow to be 0.5–1 mm in length. The tunnels must be large enough to allow neurite outgrowth, as well as enable the neuron to sense its neighbors, while at the same time small enough to prevent the neuron from squeezing through the tunnel to escape from the neurocage. Several different combinations of tunnel width and length were explored to best balance these two criteria. The chosen tunnel widths are 5  $\mu\text{m}$  and 10  $\mu\text{m}$  and the tunnel lengths are 4  $\mu\text{m}$  and 25  $\mu\text{m}$ . The desired tunnel height is between 1  $\mu\text{m}$  and 2  $\mu\text{m}$ .

### 3.1.2.1 Sacrificial Materials

The tunnels and chimneys are formed by patterning sacrificial materials. Once the Parylene-C is deposited and patterned to form the outer neurocage structure, the sacrificial materials are then removed. The most common sacrificial materials are photoresist (both soft-baked and hard-baked), silicon, and metal. The metal used is typically aluminum as it is both relatively inexpensive and easy to deposit and remove. Table 3-1 summarizes the advantages and disadvantages of these materials.

Deposition and patterning of photoresist, both soft-baked and hard-baked, is simple and small structures (less than 1  $\mu\text{m}$  wide) can be easily made. The patterning of

both the silicon and aluminum is relatively simple; however, the deposition is much more complicated, requiring sputtering or evaporation.

|                               | <b>Deposition</b> | <b>Removal</b> | <b>Thickness</b>      | <b>Usable for Chimneys</b> | <b>Usable for Tunnels</b> |

|-------------------------------|-------------------|----------------|-----------------------|----------------------------|---------------------------|

| <b>Soft-Baked Photoresist</b> | Easy              | Easy           | 0.5–100 $\mu\text{m}$ | Yes                        | Yes†                      |

| <b>Hard-Baked Photoresist</b> | Easy              | Hard*          | 0.5–100 $\mu\text{m}$ | Yes                        | Yes                       |

| <b>Silicon</b>                | Difficult         | Hard*          | < 1 $\mu\text{m}$     | No                         | Yes                       |

| <b>Aluminum</b>               | Difficult         | Medium         | < 1 $\mu\text{m}$     | No                         | Yes                       |

\* Removal agents may damage other materials and structures present.

† Requires chimneys also to be made of soft-baked photoresist. Only limited chimney heights are possible.

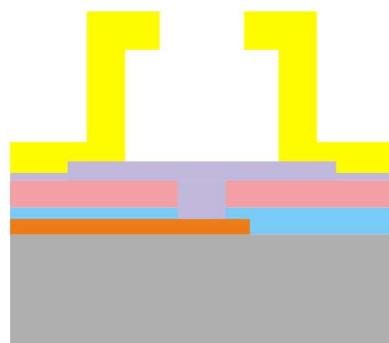

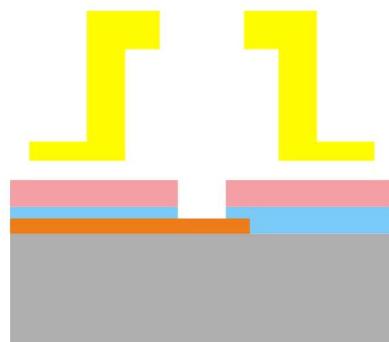

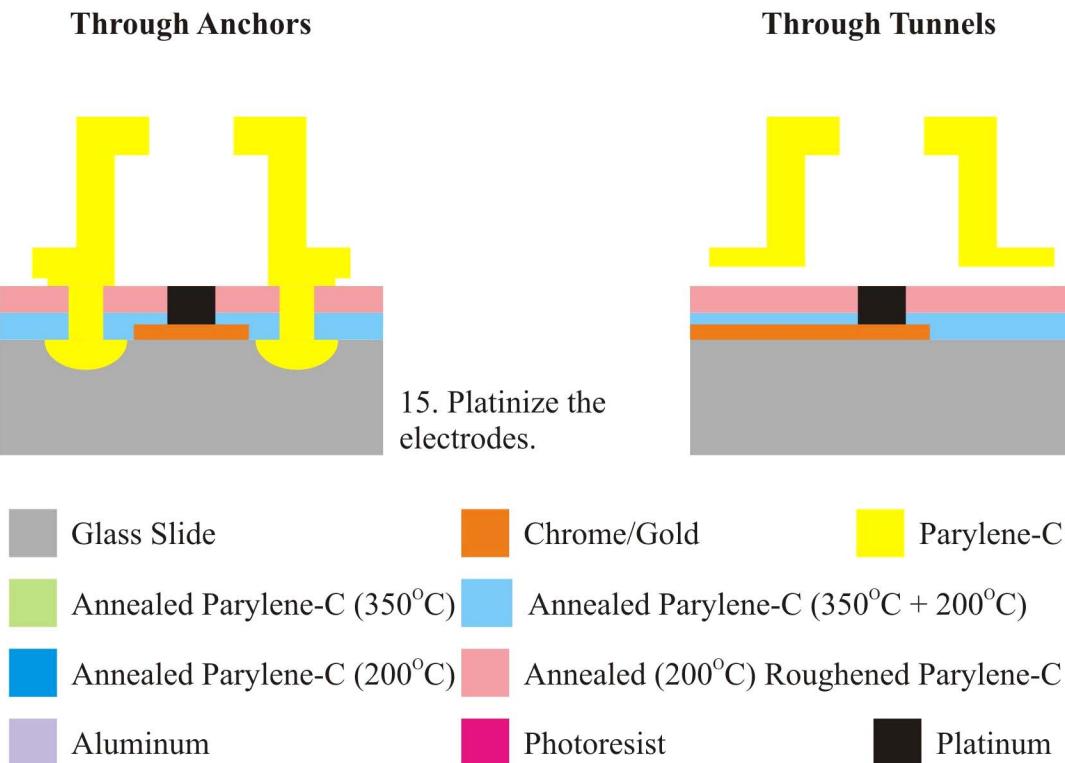

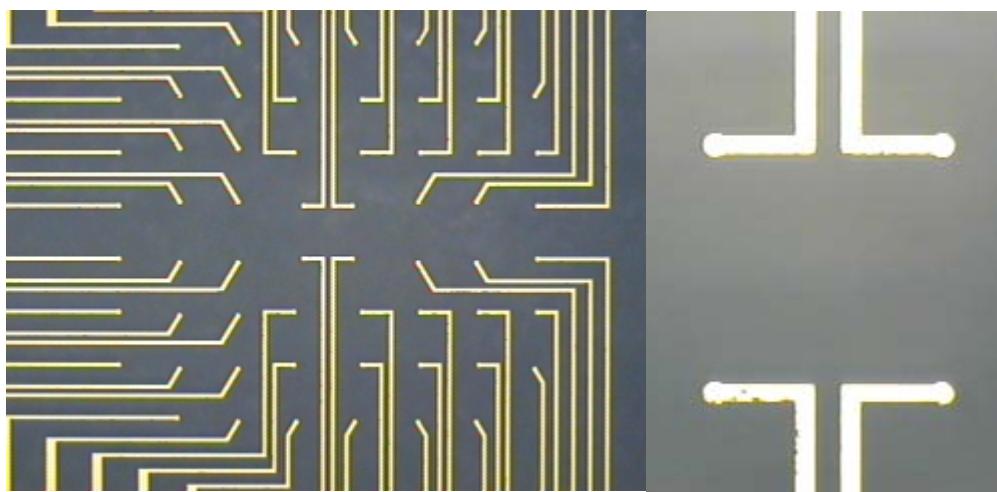

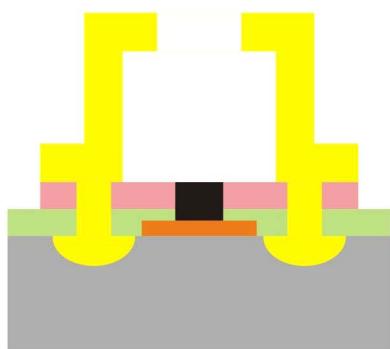

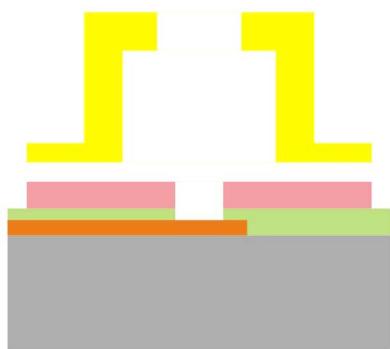

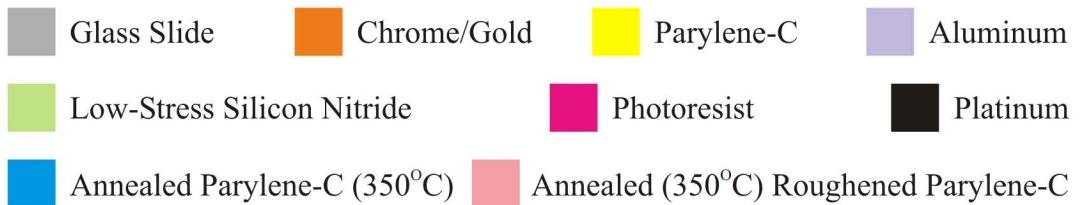

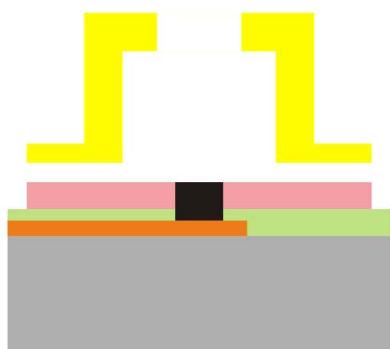

**Table 3-1.** Advantages and disadvantages of potential sacrificial materials